# Review Paper on High Speed Area Efficient Linear Convolution in Different Adder

Shubhi Shrivastava

PG Scholar

Electronics and

Communication Department

Truba College of

Science and Technology,

Bhopal

Nashrah Fatima

Assistant Professor

Electronics and

Communication Department

Truba College of

Science and Technology,

Bhopal

Paresh Rawat, PhD

Professor

Electronics and

Communication Department

Truba College of

Science and Technology,

Bhopal

## **ABSTRACT**

On this Technical era the excessive velocity and low area of VLSI chip are very- very crucial elements. Each day quantity of transistors and different active and passive elements are drastically developing on a VLSI chip. All of the processors of the gadgets adders and multipliers are playing an essential position. An adder is a pleasing element for the designing of fast multiplier. Ultimately here want a fast adder for excessive bit edition. In this paper, they carried out of linear convolution are based on ripple carry adder and array multiplier. Offering common Boolean common sense (CBL) adder presents much less additives, less path delay and better pace compare to different present CBL adder and different adders. Right here, we're evaluating the linear convolution of differentextraordinary word length from different adders. The design and experiment may be executed by way of the useful resource of Xilinx 6.2i Spartan device circle of relatives.

# **Keywords**

Common Boolean Logic (CBL), Ripple Carry Adder Linear Convolution, Xilinx

# 1. INTRODUCTION

The processor speed mostly relies upon on adder design strategies. An adder is the device with the aid of which or extra than two bit information can be added. For the excessive velocity processing of the facts transfer place has to be much less of the passive and active detail. Adder has outputs specially sum and convey. To make rapid adder carry may be reduced and changed in one-of-a-kind ways. The propagation puts off or gate delay of a gate is largely the time c programming language between the utility of the entire pulse and the incidence of the resulting output pulse. The propagation delay is a very critical function of logic circuits as it limits the rate at which they can perform. The shorter the propagation postpones, the better the speed of the circuit and vice-versa. Propagation delay has to be minimized as viable as, for high efficient addition. As an instance 4 bit addition generally propagation delay is occurring extraordinarily. When we upload one excessive bit to another high bit deliver is happening because of usually addition operation. This brings propagates to next bit and now bit addition is performed by three bit adder. So carry will propagate to the following bit over and over, this cause propagation puts off will be happening. As we've worried bits are introduced with then carry propagation postpone bits are passed off notations as. Then again propagation delay may be decreased via the resource of appropriate structural designing technique. As an example complete adder can be designed with one XOR gate, 3 AND gates and one OR gate. That kind of designing will offer 8.326 ns propagation delay. Then again full adder can be

layout via the usage of half adder and one OR gate. This type of designing will offer simplest eight.036 ns propagation delay. Convey propagation postpone can be reduced by the use of ripple bring adder, fast adder this is also referred to as appearance a-head bring generator, parallel adder, and in particular convey select adder.

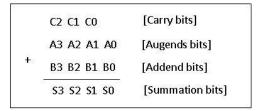

Fig 1: A Propagation delay for four bit binary addition

Nowadays, time required in multiplication manner continues to be the dominant factor in determining the practice cycle time of a DSP chip [3]. Historically shift and add set of rules is getting used for designing. But, this isn't always suitable for VLSI implementation and additionally from postpone point of view. a number of the important algorithms proposed in literature for VLSI implementable fast multiplication are booth multiplier, array multiplier and Wallace tree multiplier [4]. Despite the fact that these multiplication techniques had been effective over traditional "shift and upload" approach, but their disadvantage of time consumption has no longer been absolutely eliminated. Vedic arithmetic provides a unique solution for this hassle. The Baugh-Wooley multiplication is one of the efficient methods to handle the sign bits. This approach has been developed in order to design regular multipliers, suited for 2's complement numbers [2]. Let two nbit numbers, multiplier (A) and multiplicand (B), to be multiplied.

# 2. LITERATURE REVIEW

Rashmi K. Lomte et al., (2011, [1]), convolution and Deconvolution has many applications in digital signal processing. Multipliers and dividers are primary blocks in convolution and deconvolution implementation. They consume much of the time. With advances in technology, many researchers have tried and are trying to layout multipliers and dividers which provide both of the following-high pace, low power consumption, regularity of layout and as a result much less region or maybe mixture of them in multiplier and divider. in this paper, the direct method is used to locate convolution and deconvolution. Discrete linear convolution of finite period sequences the usage of Urdhva Triyagbhyam set of rules is provided here. Same set of rules is likewise used for deconvolution to enhance velocity. This

design method successfully and accurately hastens computation without compromising with region.

Prof J M Rudagi et al., (2011, [2]), Multiplication is an vital essential feature in mathematics operations. Multiplicationbased totally operations together with Multiply and gather(MAC) and inner product are among a number of the regularly used computation extensive functions(CIAF) presently applied in many digital sign Processing (DSP) programs such as convolution, fast Fourier rework(FFT), filtering and in microprocessors in its arithmetic and common sense unit . Considering multiplication dominates the execution time of maximum DSP algorithms, so there is a want of high velocity multiplier. Presently, multiplication time remains the dominant component in figuring out the instruction cycle time of a DSP chip.

Akhalesh K. Itawadiya et al. (2013, [3]), digital signal Processing (DSP) operations are very important part of engineering as well as medical area. Designing of DSP operations have many strategies. For the designing of DSP operations, multiplication is play crucial function to carry out sign processing operations which includes Convolution and Correlation. The new methods of this implementation are mentally and clean to calculate of DSP operations for small duration of sequences. On this paper a fast approach for DSP operations based totally on historic Vedic mathematics is contemplated.

Surabhi Jain et al. (2014, [4]), In digital signal Processing, the convolution and deconvolution with a totally long collection is ubiquitous in lots of application areas. The basic blocks in convolution and deconvolution implementation are multiplier and divider. They devour an awful lot of time. This paper offers a right away method of computing the discrete linear convolution, circular convolution and deconvolution. The approach is simple to study due to the similarities to computing the multiplication of two numbers. The maximum enormous factor of the proposed technique is the development of a multiplier and divider architecture based on historic Indian Vedic arithmetic sutras Urdhvatriyagbhyam and Nikhilam algorithm. The outcomes show that implementation of linear convolution and circular convolution the usage of vedic mathematics is efficient in terms of region and pace as compared to their implementation the use of traditional multiplier & divider architectures. The coding is executed in VHDL. Simulation and Synthesis are carried out the use of Xilinx ISE layout suit 14.2.

# 3. DIFFERENT TYPES OF ADDER

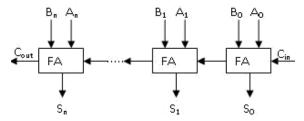

Ripple carry is a combinational circuit for adding greater than two bit records. It's also known as parallel adder. Ripple carry adder can be designed with the aid of the use of complete adder in cascading shape. Convey output of first full adder is hooked up with enter of the subsequent full adder, so bring is rippled from one adder to some other adder. This is by way of it is referred to as ripple-bring adder. Let us take example, for designing n bit RCA inputs are  $(A_n ... A_3, A_2, A_1, A_0)$  and  $(B_n \dots B_3, B_2, B_1, B_0)$  then carry bits  $(C_n \dots C_3, C_2, C_1)$  and summation bits are  $(C_{out} ... S_3, S_2, S_1, S_0)$ .

Fig 2: An n-bit Ripple Carry Adder bit binary addition

In this figure all the full adders are connected in cascading form. Bring enter is a further enter which has fixed price. First complete adder gives the convey output and summation output. Convey output of the primary complete adder is hooked up with 2nd cascading complete adder so that you can be taken into consideration as an enter bit.

$$S_0 = (A_0 \oplus B_0) \oplus C_{in} \tag{1}$$

$$S_1 = (A_1 \oplus B_1) \oplus C_1 \tag{2}$$

$$S_1 = (A_1 \oplus B_1) \oplus C_1$$

$$C_{out} = (A_n.B_n) + (C_n.B_n) + (A_n.C_n)$$

(2)

### **Kogge Stone Adder**

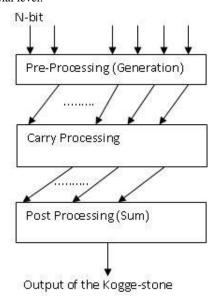

Kogge Stone Adder changed into proposed by using Peter M. Kogge and Harold S. Stone. Kogge Stone Adder is a complicated generation of look a- head conveys Adder. That is also known as parallel prefix adder. It has more area than to Brent Kung Adder however less Fan-out. This adder affords the deliver sign time and turn out to be quickest adder for commercial level.

Fig 3: A Block Structure of Kogge Stone Adder bit binary addition

First block of KSA is Pre- Processing a good way to generate and propagate the convey. Processing of deliver may be carried out over the convey processing place and all the bring sign go through the publish processing block. Inside the pre preprocessing level we find the, generate and propagate alerts from every inputs.

$$P_n = A_n \oplus B_n \tag{4}$$

$$G_n = A_n \cdot B_n \tag{5}$$

Carry processing stage provides the carries corresponding to each bit. Execution of these bit operation is carried out from parallel. After finding the carries in parallel they are segmented in to smaller pieces.

$$CP_{n-1} = P_{n-1} \oplus P_n$$

(6)

$CG_{n-1} = (P_n \oplus G_{n-1}) + G_n$  (7)

Bottom block is summation block which provides the summation bits. That blocks are comprised with XOR gate. If one input isn't the same as any other then output will be excessive. And if inputs are identical then outputs can be low. Kogge Stone presents the less region than to other parallel adder like deliver choose adder, convey keep adder and appearance in advance adder.

Fig 4: A Functional Diagram of Kogge Stone Adder Stone Adder bit binary addition

Above diagram is a functional diagram of Kogge Stone adder for 4 bit addition. Here elliptically symbol defined as a carry processing stage. The output of the preprocessing stage is fed to next carry stage and post processing as well.

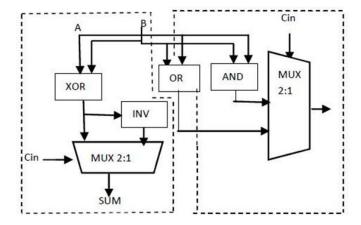

# • Modified Common Boolean Logic Adder

Area and power efficient excessive speed facts logic path are the most enormous regions of studies. With the help of simple change in gate level we will obtain the development inside the effects. velocity of the adder depends on the time required to propagate the bring thru the adder, those adder works in series layout, this is the sum of the primary position bit is calculated while the preceding bits are summed and the convey is propagated to that subsequent level.

Carry select adder (CSLA) is one of the superior adders used in information processing processors to perform fast arithmetic function. It specializes in the hassle of bring propagation put off through producing the deliver independently at each degree and the pick out the efficient one with the assist of multiplexer to perform the sum. The traditional CLSA is RCA (Ripple carry adder) which generate the partial sum and carry by way of the use of the enter deliver circumstance Cin=zero and Cin=1, select one out of each pair to shape final sum and final convey output.

RCA isn't location efficient as huge wide variety of gates circuitry is used to form the partial merchandise after which the final sum and convey is selected.

Another shape of CLSA adder makes use of binary to excess-1 convertor changing ripple deliver adder with Cin=1. This adder is known as CLSA at the side of BEC. The range of gates used has been reduced while we must layout big bit adder. This adders is more conventional as examine to RCA

while cope with silicon vicinity used however that is having marginally higher put off time.

The proposed not unusual Boolean logic (CBL) adder is placepower-put off efficient. It paintings on the good judgment to get rid of the redundant adders and use commonplace Boolean common sense as examine to standard deliver pick adder.

The CBL block is constructed from two components sum technology block and carry era block. In sum generation block the output sum is completed using the multiplex. This multiplex is used to choose the output cost depeding at the value of Cin( previous bit).

If Cin=0, then output is xor of the two enter bits. If Cin=1, then output get inverted. In deliver generation block, multiplexer is used to pick out the delivery of next degree relying upon the previous carry enter. If Cin=0, cout is OR of two input and if Cin=1 the output deliver is AND of the input bit.

Figure 5: Block Diagram of CBL

If

$$C_{in} = 0$$

$Sum = A XOR B$

$Carry A OR B$

$else$

$Sum = NOT (A XOR B)$

$Carry = A AND B$

This same process is used for the n number of bits and thus we get the final sum and carry as output.

## 4. LINEAR CONVOLUTION

Complex logical designing can be reduced by the array mathematics calculation which is consisting with 16 sutras. Number of fan in, fan out pin and input output buffers can be minimized by using these array mathematics sutras. For the high speed convolution, multiplier and adder must be high efficient and low area as possible as. For instance (A3, A2, A1, A0) and (B3, B2, B1, B0) are the finite length sequence.

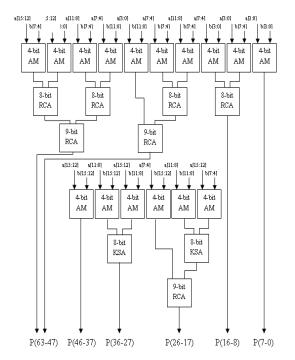

For the appropriate output we can use the 4 bit array multiplier, 8 and 9 bit ripple carry adder. Multiplication of convolution input sequence is different from ordinary binary multiplication.

Figure 6: Linear Convolution based on array multiplier and RCA adder

### 5. METHOD OF DESIGN

- Design linear convolution using signed and unsigned multiplier.

- Design linear convolution using different types of adder and compared.

- Design linear convolution using different types of input and compared existing algorithm.

- Hand calculation of delay and area in linear convolution in different inputs.

- All the modules design to different device family i.e. Spartan-3, Virtex-4 and Virtex-7.

# 6. SIMULATION ANALYSIS

Simulation of these experiments can be done by using Xilinx 14.2I VHDL tool. In this paper we are focusing on propagation delay. Propagation delay must be less for better performance of digital circuit. Xilinx is an analysis and simulation tools which has many application in research filed. In this tool simulation is divided in to three categories, model, behavioral and structural. Xilinx 14.2i is an updated version which has many merits than other version.

### 7. CONCLUSION

Conclusion of this paper is that, designed a low power and less area or minimum propagation delays CBL Adder. According above table (see Table 1) ripple carry adder and other parallel adder has more number of slices than to CBL. Proposing high efficient CBL adder can be used for baugh multiplication to design high speed linear convolution. Apart from that it can be used in high speed convolution methods all the experiment has done in Spartan, Xilinx 14.21 VHDL package.

### 8. REFERENCES

- [1] Jain, S.; Saini S. "High Speed Convolution and Deconvolution algorithm (Based on Ancient Indian Vedic Mathematics) electrical engineering/electronics, computer, telecommunication and information technology (ecti-con), 2014 11th international conference on doi: 10.1109/ ecticon.2014.6839756 Publication Year: 2014, Page(s): 1 – 5.IEEE 2014.

- [2] Lomte, Rashmi K., and P. C. Bhaskar. "High Speed Convolution and Deconvolution Using Urdhva Triyagbhyam." VLSI (ISVLSI), 2011 IEEE Computer Society Annual Symposium on. IEEE, 2011.

- [3] Itawadiya, Akhalesh K., et al. "Design a DSP operations using vedic mathematics." Communications and Signal Processing (ICCSP), 2013 International Conference on. IEEE, 2013.

- [4] L. Sriraman, T.N. Prabakar, "Design and Implementation of Two Variable Multiplier Using KCM and Vedic Mathematics," 1st Int. Conf. on Recent Advances in Information Technology, Dhanbad, India, 2012, IEEE Proc., pp. 782-787.

- [5] Soma BhanuTej, 2012.Vedic Algorithms to develop green chips for future, International Journal of Systems, Algorithms and Applications, Volume 2, Issue ICAEM12, ISSN Online: 22772677..

- [6] Youngjoon Kim and Lee-Sup Kim, 2001.A low power carry select adder with reduced area, IEEE International Symposium on Circuits and Systems, vol.4, pp.218-221. Tavel, P. 2007 Modeling and Simulation Design. AK Peters Ltd.

- [7] Akhilesh Tyagi,1990.A Reduced Area Scheme for Carry-Select Adders,IEEE International Conference on Computer design, pp.255-258.

- [8] Belle W.Y.Wei and Clark D.Thompson,1990.Area-Time Optimal Adder Design, IEEE transactions on Computers, vol.39, pp. 666675.

*IJCA™*: www.ijcaonline.org