# **Memristor Theory and Mathematical Modelling**

# Ezeogu Apollos

Scholar, National Information Technology Development Agency

# ABSTRACT

Memristor is the newly discovered fourth circuit element. The other familiar three circuit elements are resistor, capacitor and inductor. In 1971, Leon Chua reasoned that there should be a fourth circuit element on the ground of symmetry that gives a relationship between flux and charge. He named it memory resistor, abbreviated as memristor. The first experimental manufacture of this fourth element was published in May 2008 by HP researchers team led by Stanley Williams. Afterwords, researchers have been exploring memristor and its possible applications. Thus, this report studies and presents the general theory of memristor, classification of memristor, the I-V characteristics, the non volatility memory, the switching mechanism for bipolar switching in  $TiO_2$ , the mathematical models of memristor including the various window functions; and also potential applications of memristor. Meanwhile, where necessary simulation are carried out using Cadence Virtuoso design tool and VerilogA for modelling the memristor for simulation purpose.

## **General Terms**

Memristor Theory, Mathematical Model, Window Function

#### Keywords

Memristor, Hysteresis loop, I-V characteristics, Linear model, Non linear model, Exponential model, Simmons Tunel Barrier Model, TEAM Model

# 1. INTRODUCTION

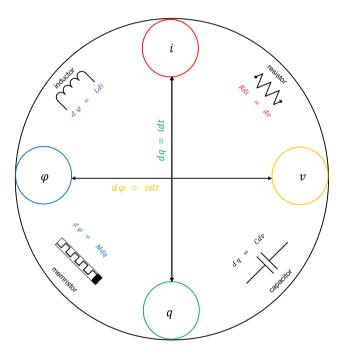

Prof. Leon Chua in 1971 first proposed that there should be a fourth circuit element in order to complete the 360 degree geometry as shown in Figure 1. He named this element, memristor[1, 2]; because the resistance seems to remember or memorize the charge that has passed through it hence the term "memristor". Then in 2008, Stan Williams and his group in the Information and Quantum Systems (IQS) Lab at Hewlett Packerd (HP) fabricated the first memristor using a nano-scale thin film device[4]: and also Dmitri Strukov et al. [6, 7] demonstrated the characteristics of memristor by given the mathematical and physical model describing the memristor as equivalent to a time-dependent resistor whose value at time, t, is linearly proportional to the amount of charge, q(t), that has flown through it as shown in equation 1 and 2. And also from Figure 1, the relationship between all the electrical elements is established. Thus in electrical engineering, only inductor, capacitor and resistor have been explored to a large extend; however, the memristor element is now newly been explored and hope to be of wide application in the field of computing, electrical and electronic engineering/technology [3].

Fig. 1. The Complete Four Circuit Elements [3]

Memristor has variety of potentials such as creating non volatile Static Random Access Memory [3]; Building neuromorphic architecture; reliable memristive gas sensing [18], logic multi function design [19]; Memristor-based physical unclonable function; memristor-based Computation-in-Memory architecture; Memristive self- reparable system; Computer-Brain Interface; Brain-Computer Interface, Brain-Brain Interface; Disposabel sensors, and many medical applications in the nearest future technology.

# 2. MEMRISTOR THEORY

#### 2.1 What is Memristor?

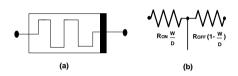

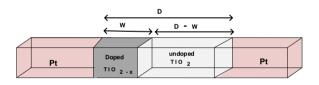

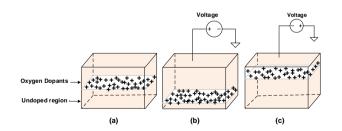

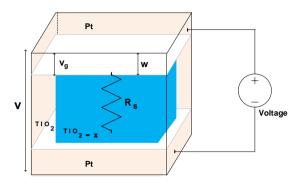

The word "memristor" fully means "memory resistor"; it is a passive component which relates charge and magnetic flux. Memristor is any 2-terminal passive device that exhibit a pinched hysteresis loop been driven by any periodic input current source, or voltage source, with zero DC component[5]. Hence when a charge, q, flows between the two terminals, a magnetic flux,  $\Phi$ , is created. The HP memristor model comprises of a very thin titanium oxide,  $TiO_2$ , which is sandwiched between two platinum (Pt) contacts (see Figure 3). Thus, the oxygen-deficient titanium dioxide,  $TiO_{2-x}$  where x is about 0.05, is heavily doped with positively charged oxygen atoms while the other part remains undoped [8]; then when a positive electric potential is applied, the positive oxygen vacant ions drift toward the (black bar of the symbol in figure 2(a)) undoped  $TiO_2$  layer due to the repulsive force that exist between them and the positive potential - because like charges repel each other this then narrows the potential barrier and decreases the length of the undoped region thus decreasing the resistance until it reaches a minimum threshold thereby making the material conductive (ON). However, if a negative field is applied the oxygen atoms will all be drifted away from the  $TiO_2$  layer back to their original position - opposite charges attract each other - thus restoring the device thereby increasing the thickness of the  $TiO_2$  layer and in consequence the resistance thereby turning it OFF.

Thus, when an applied voltage is removed the charged Tiions do not move or drift therefore making the boundary of the doped and undoped layer of  $TiO_2$  fixed such that when later a voltage is applied it starts from the previous state where it had left – this is why it is said to be non-volatile.

Fig. 2. (a) Memristor Symbol (b) Equivalent Resistor Model [3]

Fig. 3. HP Memristor Model [3]

Fig. 4. HP Memristor Behaviour When Positive and Negative Voltages are Applied [3]

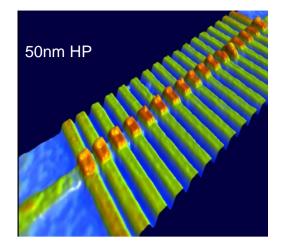

Fig. 5. HP Micrograph Array of Memristor Devices (Adapted from [9])

#### 2.2 Current, Voltage, Charge and Flux Relationship

Memristor can either be Current, Voltage, Charge or Flux controlled as derived in equations (1) through (4): Given that,

$$M(q) = \frac{d\psi}{dq}$$

Charge controlled (1)

$$W(\psi) = \frac{dq}{d\psi}$$

Flux controlled (2)

$$I(t) = W(\psi(t))V$$

Current controlled (3)

$$V(t) = M(q(t))I$$

Voltage controlled (4)

Where M is called the memristance, and its S.I unit is ohms  $(\Omega)$ . Thus, when M does not vary, then the memristor behaves as a resistor. And W is called the memductance, and its S.I unit is Rho  $(\Omega^{-1})$ .

The memristance, M, of a memristor is the functional relationship between charge and magnetic flux. This increases when electric current flows through the memristor in one direction and decreases whent the electric current flows in the reverse direction. Then when power is shut down, the electrical resistance freezes until power is restored then the memristor will remember the last state of the resistance; this is the unique property of the memristor and this property is the essence of its non-volatility which makes it suitable for many application such as resistive memory(ReRAM) or non volatile Memristive Static Random Access Memory(MSRAM) [3]; Soft computing; neurocomputing; Self-reparable system; and many others.

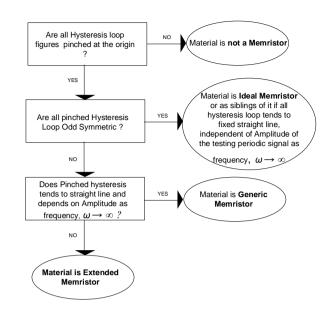

#### 2.3 Memristor Classification

It was shown in paper [5] that the input can be current source or voltage source controlled. And through the pinched hysteresis loop fingerprint, we can classify memristor material or devices. Many materials have been found to exhibit memristive property; such as amoeba, squids, human neurons, dye solar cells and electron spun materials. Memristor has been classified into four classes, namely: Ideal Memristor, Ideal generic, Generic and Extended Memristor

[5]. In any case, the ideal memristor and its siblings exhibit pinched hysteresis loop driven by a half-wave odd-symmetric input voltage source, or current source, which is odd-symmetric, and crosses each other with distinct slopes at the origin provided that the loci is double-valued in a small neighborhood of the origin [5]. Another classification scheme, which is the universal scheme called " the coincident zero-crossing memristor signature, more detail of this scheme can be found in the works of Prof. Chua Leon's paper [5]. In the paper it states that:

The waveform of the voltage v(t) (resp., current i(t)) associated with the current i(t) (resp., voltage v(t)) of any admissible signal pair (i(t), v(t)) (resp.,(v(t), i(t)) measured from the memristor setup either with current or voltage source must cross the time axis whenever i(t) = 0 (resp., v(t) = 0).

Therefore, it follows from the conclusion of [5] that the pinched hysteresis loops of all passive memristors are restricted to the first and the third quadrants of the v-i plane; hence the zero-crossing times of both i(t) and v(t) of passive memristors are identical. In addition, the phase shift of the periodic current and voltage waveforms  $i_{(t)}$  and  $v_{(t)}$  of the same frequency input will have a phase shift of zero.

| Table 1. | Memristor | Classification | Idea A | Adapted : | from | [5] | ) |

|----------|-----------|----------------|--------|-----------|------|-----|---|

|          |           |                |        |           |      |     |   |

| MEMRISTOR GENEALOGY        |                                                                |                                                                    |  |  |  |

|----------------------------|----------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

|                            | Current Control                                                | Voltage Control                                                    |  |  |  |

| EXTENDED<br>MEMRISTOR      | $V = R(x, i)i$ $R(x, 0) \neq \infty$ $\frac{dx}{dt} = f(x, i)$ | i = G(x, v)v<br>$G(x, 0) \neq \infty$<br>$\frac{dx}{dt} = g(x, v)$ |  |  |  |

| GENERIC<br>MEMRISTOR       | $V = R(x)i$ $\frac{dx}{dt} = f(x, i)$                          | $i = G(x)v$ $\frac{dx}{dt} = g(x,v)$                               |  |  |  |

| IDEAL GENERIC<br>MEMRISTOR | $V = R(x)i$ $\frac{dx}{dt} = \hat{f}(x)i$                      | $i = G(x)v$ $\frac{dx}{dt} = \hat{g}(x)v$                          |  |  |  |

| IDEAL MEMRISTOR            | $V = R(q)i$ $\frac{dq}{dt} = i$                                | $i = G(\varphi)v$ $\frac{d\varphi}{dt} = v$                        |  |  |  |

## 2.4 Memristor Properties

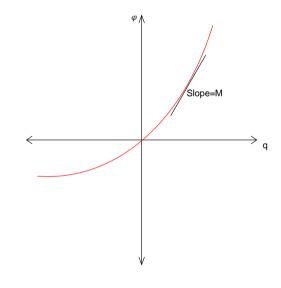

2.4.1 Flux-Charge Relation:. The flux to charge relation of a memristor has a monotonic increasing property as seen in figure 7. The slope of the graph gives the memristance, M. The Memristance defines the passivity of the memristor. The memristance is greater than or equal to zero always which proves its property as passive element.

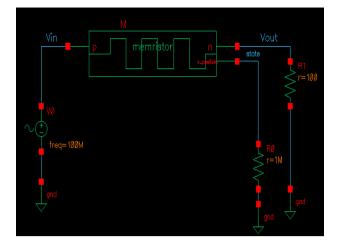

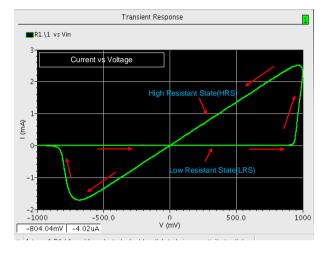

2.4.2 Memristor I - V Characteristics:. The I - V characteristics show the current-voltage relationship of the memristor just as we have in p-n junction diodes. It is state variable dependent and also frequency dependent - that is, time derivative of the state variable. Thus, in this paper, the memristor was modelled using VerilogA by including the created symbol and typing on the switch view list spectre cmos<sub>s</sub>ch veriloga schematic in the Cadence Virtuoso Design tool to run the simulation correctly without errors [3]. The I-V characteristics, state variable wave form showing  $R_{ON}$  and  $R_{OFF}$  switching with respect to time were plotted. This VerilogA SPICE model included the linear, non linear, exponential

Fig. 6. Memristor Classification Test Algorithm(Idea adapted from[5])

Fig. 7. Flux-Charge Relation

model and the window functions such as Strukov et al. Biolek, and Joglekar et al. models which provide us with a windowing function for the non-linear drift behaviour for the state variable control; this will be discussed in detail in the next section dealing with memristor modelling.

The pinched hysteresis loop that looks like the mathematical infinity symbol with the center at the zero axis in the I-Vcharacteristics indicates that the voltage is increased from zero to a positive maximum value, thereafter decreased to a minimum negative value and finally returned to zero.

2.4.3 *Memristor Switching Mechanism:*. A memristive switch needs to be at least 1000 times as resistive to the flow of current as

Fig. 8. Simulation Schematic Setup [3]

Fig. 9. Memristor I – V Characteristics Hysteresis Loop [3]

it was in its ON state[8]. This total change in the resistance value is dependent on length of time voltage is applied. Thus, the longer an applied positive voltage, the lower the resistance until it reaches a minimum value. Whereas, the longer a negative voltage is applied, the higher the resistance until it reaches a maximum value. Consequently, if the applied voltage is removed, then the device resistance remains constant at that state until been reset by applying a reverse voltage. Therefore a positive voltage will switch the device ON while a negative voltage will switch it OFF. Note that *pushing the memristor from the ON state towards the OFF state is always slower than driving in the other direction especially at low voltage* (*read voltage*) [9].

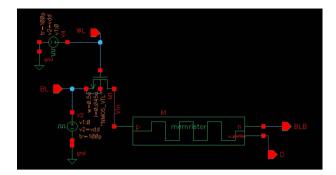

The configuration in figure 10 shows how the memristor is connected to the 1T transistor which acts as an access for writing data to or reading from the memristor. In this state, data can be read or written into the memristor, therefore making it act as a backup storage device when power is turned off. The sinusoidal wave form in figure 11 shows how writing can be done in memristor. A positive wave turns it ON, thus " 1" is written while a negative wave turns it OFF, thus a "0" is written into the memristor.

Fig. 10. Schematic for Memristor Switching [3]

Fig. 11. Memristor Switching Mechanism [3]

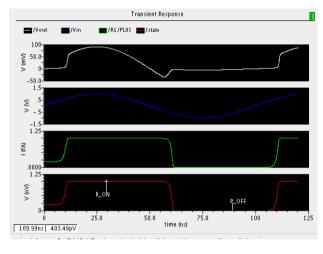

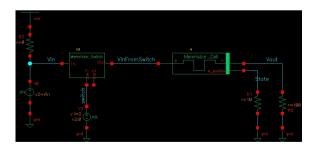

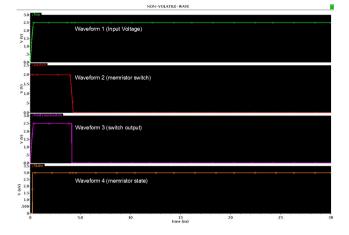

2.4.4 Memristor Non Volatility:. Memristor exhibits nonvolatility when power is cutoff as demonstrated via the schematic and simulation in figure 12 and 13 respectively. The first 4ns shows a high input voltage (waveform 1), a ON switch (waveform 2), a high switch output (waveform 3) and the memristor switching from HRS (OFF) to LRS (ON) (waveform 4). When the switch goes OFF after 4ns and power supply to the memristor is cut off, the memristor still retained its previous high state[20].

Fig. 12. Non Volatility Schematic TestBench [20]

Fig. 13. Retaining HIGH state after power cuttoff [20]

# 3. MEMRISTOR MODELLING

#### 3.1 Linear Model

The linear ion drift model by Strukov etal in [6] was the original model that HP labs modeled its memristor on when they first announced the physical realization of the device in 2008. Thus, referring back to figure 2b and and figure 3, the length of the doped region  $TiO_{2-x}$ , with its oxygen charge +2 ionic dopants, changes in response to the applied voltage and therefore alters the effective resistance of the memristor. That is, when a voltage or current is applied to the device, the interface between the  $TiO_{2-x}$  and  $TiO_2$ layers shifts according to the amount of applied voltage, therefore altering the resistance between the two electrodes. Here, the mathematical model is derived by depicting D and w to represent the thickness of the sandwiched region and the doped region with high conductivity in the  $TiO_2$  memristor respectively, and let  $R_{ON}$  and  $R_{OFF}$  be the resistances of the doped and undoped regions respectively (see figure 3). The linear drift model supposses that the state variable,  $x_t$  is proportional to the charge flowing across the memristor; then the effective resistance (memristance) is given as,

$$M_{(w)} = \frac{v_{(t)}}{i_{(t)}} = \left(R_{ON}\frac{w_{(t)}}{D} + R_{OFF}\left(1 - \frac{w_{(t)}}{D}\right)\right)$$

(5)

where  $x = \frac{w_{(t)}}{D}$  is called the "state variable" defined as,

$$x = \frac{w_{(t)}}{D} = \mu_v \frac{R_{ON}}{D^2} q_{(t)} \quad where \ x \epsilon[0, D] \tag{6}$$

and  $\mu_v$  is the mobility of the oxygen dopant ions.

Substituting equation 6 into equation 5, we have the memristance given as:

$$M_{(w)} = \left(R_{ON}\mu_v \frac{R_{ON}}{D^2}q_{(t)} + R_{OFF}\left(1 - \mu_v \frac{R_{ON}}{D^2}q_{(t)}\right)\right) \quad (7)$$

Rearranging and simplifying, we have

$$M_{(w)} = \mu_v q_{(t)} \left(\frac{R_{ON}}{D}\right)^2 + R_{OFF} \left(1 - \mu_v \frac{R_{ON}}{D^2} q_{(t)}\right)$$

(8)

Thus, if the value of the  $R_{ON}$  is negligible such that  $R_{ON} \ll R_{OFF}$  Then, the Memristance is simplified to:

$$M_{(w)} = R_{OFF} \left(1 - \mu_v \frac{R_{ON}}{D^2} q_{(t)}\right)$$

(9)

This model is known as the *linear drift model* because the velocity of the width (w) is linearly proportional to the current. In other words, the change to the memristor state would be the same regardless voltage waveform so far the net flux is the same across the memristor. And also when voltage is applied, the state of memristor will move back to the initial position if the net flux induced is zero. Furthermore, the simplified equation relating current and voltage can now be defined by:

$$M_{(w)} = \frac{v_{(t)}}{i_{(t)}} = R_{OFF} \left(1 - \mu_v \frac{R_{ON}}{D^2} q_{(t)}\right)$$

(10)

Memristor exhibits the pinched hysteresis loop in the current versus voltage (I-V) characteristics when a sinusoidal voltage input is applied. Thus, the resistance of the device depends upon the past history of the input current or voltage [10].

## 3.2 Nonlinear Model

It is known that the memristor also exhibits nonlinear behaviour due to the fact that the *linear model* does not take into account the boundary effect. The boundary between the doped and undoped regions moves with a drift velocity of  $\mu_D$  which decreases as it gets closer to the edge,  $w \sim 0$  and  $w \sim D$ ; and also it does not take into account the large non-linearity of the electric field inside the memristor. Thus, Joglekar and Wolf [11] developed a modified mathematical model to account for this effect, this is known as the *nonlinear drift model*. The following conditions needs to be met for a window function for modelling the non linearity [15]:

- —The top and bottom electrode boundary of the memristor must be taken into account

- —The function must consider linkage betweent the linear and non linear drift top and bottom electrode boundary must be taken into account

- -The function must be scalable

- —The function must have control parameter to set the model desired.

Therefore, equation 6 is modified to,

$$\frac{w_{(t)}}{D} = \mu_v \frac{R_{ON}}{D^2} q_{(t)} f(x)$$

(11)

Where  $x = \frac{w(t)}{D}$  and f(x) is called the *window function* which bounds the state variable within zero and infinity[12], defined by the following window functions:

*3.2.1 Joglekar's Window Function:*. Joglekar's window function can be given as:

$$f(x) = 1 - (2x - 1)^{2p} \tag{12}$$

The constant p in equation 12 is a positive integer for parameterizing a family of window functions. Thus, as p is increased, the rate at which the mobility of the oxygen vacancies is suppressed decreases considerably to a p = 10 unless when w is approximately 0 or D because as stated earlier mobility,  $\mu_D$ , is drastically reduced at these boundaries. This control parameter, p, controls the linearity of the model, whereby it becomes more linear with increase in p.

3.2.2 Biolek Window Function:. Biolek et al.[13] proposed another window function that allows the memristor to retract from the deadend state. The window function is modelled to accommodate the fact that a reversed bias should move back the state variable after it reaches either boundary and also the boundary speeds are different in each voltage bias direction. In other words, it is not only state variable dependent but also current flow through the memristor. Therefore, this is described by a current dependent step function, stp(-i), which is part of a new window function  $f(\frac{w(t)}{D}) = f(x)$ , defined as,

$$f(x) = 1 - (x - stp(-i))^{2p}$$

(13)

where, stp(-i) = 1 if  $i \ge 0$  and stp(-i) = 0 if i < 0

3.2.3 Prodromakis Window Function:. Prodromakis et al.[15] expanded Strukov's window function,  $x - x^2$ , which is based on smooth parabolic curve by using the method of completing the square and also included a control parameter as an exponent to yield scalability and flexibility in window function,

$$f(x) = j(1 - [(x - 0.5)^2 + 0.75]^p)$$

(14)

where  $0 \le f(x) \le 1$ , p and j are real number unlike the restricted integer type for p in Biolek and Joglekar window functions. The value of j is the control parameter. The challenge with this window function is that it does not address the issue with boundary lock [21].

3.2.4 Zha's Window Function:. The window function, f(x), by Zha et al. resolves issues of boundary lock, scalability, and nonlinear effects simultaneously[21]. Zha's window function is defined as follows:

$$f(x) = j(1 - [(0.25(x - stp(-1))^2 + 0.75]^p)$$

(15)

where stp(i) is given in Equation 15 and p and j are positive real numbers [21].

# 3.3 Exponential Model

The nonlinear model defined in equations 12 to 15 still does not account for the non-linearity due to the large electric field within a memristor. Thus, the *exponential model* takes this effect into account. Yang et al [14] quantified the I-V characteristic approximated to,

$$i_{(t)} = x_{(t)}^{n}\beta sinh(\alpha v_{(t)}) + \chi(exp(\gamma v_{(t)}) - 1)$$

(16)

where  $\beta$ ,  $\alpha$ ,  $\chi$ ,  $\gamma$  are constants that need to be determined; and n is a free parameter that determines the effect of the state variable on the current. While at OFF-state, the I-V curve behaves like a P-N junction, that is the exponential part, then at ON-state the I-V curve follows a tunneling process[10], that is the hyperbolic function *sinh* part of the equation. The equation of the state variable can be written as:

$$\frac{dx}{dt} = a.v_{(t)}^n f(x) \tag{17}$$

where f(x) is the window function; a and n are constant and  $v_t$  is voltage.

#### 3.4 Simmons Tunnel Barrier Model

The above models described are based on the HP models which consist of two regions modelled as resistance in series. Whereas, Pickett et al. presented another physical model of the memristor as an alternative to the HP model, consisting of a resistor and an electron tunnel barrier in series [16]. This model assumes an asymmetric and non-linear switching behaviour because of the exponential dependence of ionized dopants.

#### Fig. 14. Simmons Tunnel Barrier Model

The derivative of the state variable is given as:

$$\frac{dw_{(t)}}{dt} = F_{off} sinh(\frac{i}{i_{off}}) exp[-exp(\frac{w-a_{off}}{w_c} - \frac{|i|}{b}) - \frac{w}{w_c}], i > 0$$

(18)

$$\frac{dw_{(t)}}{dt} = F_{on}sinh(\frac{i}{i_{on}})exp[-exp(\frac{w-a_{on}}{w_c} - \frac{|i|}{b}) - \frac{w}{w_c}], \ i < 0$$

(19)

Where the parameters as follows:

$F_{off}, F_{on}, a_{off}, a_{on}, i_{off}, i_{on}, and b, w_c$  are fitting parameters; while  $F_{on} >> F_{off}$ ; and the  $F_{on}$  is used in tweaking w; then  $i_{off}, i_{on}$  used for confining the current threshold to certain limit. And  $a_{off}, a_{on}$  force the upper and lower bound of w. The I-V characteristics can be defined by:

$$i_{(t)} = \frac{j_0 A}{\Delta w^2} [\phi_1 exp^{-B(\phi_1)^{0.5}} - (\phi_1 + e|v_g|)exp^{-B(\phi_1 + e|v_g|)^{0.5}}$$

(20)

Where A is the barrier cross- sectional area and  $j_0$ ,  $\Delta w$ , B and  $v_g$  are all defined as follows:

$$j_0 = \frac{e}{2\pi h} \tag{21}$$

$$B = \frac{4\pi\Delta w(2m)^{0.5}}{h} \tag{22}$$

$$\phi_1 = \Phi_0 - e|v_g| \left(\frac{w_1 + w_2}{w} - \left(\frac{1.15\lambda w}{\Delta w} ln\left(\frac{w_2(w - w_1)}{w_1(w - w_2)}\right)\right)$$

(23)

And also,

$$w_1 = \frac{1.2\lambda w}{\phi_0} and\Delta w = w_2 - w_1 \tag{24}$$

$$w_2 = w_1 + w(1 - \frac{9.2\lambda}{3\phi_0 + 4\lambda - 2e|v_g|})$$

(25)

$$\Lambda = \frac{e^2 ln(2)}{8\pi k \epsilon_0 w} \tag{26}$$

Where k is the dielectric constant,  $\epsilon_0 = 8.854 \times 10^{-12} F/m$  is the permitivity of free space.

2

$$v_{(g)} = v - v_{(R)} = v - i_{(t)} R_{(s)}$$

(27)

Where  $e = 1.6 \times 10^{-19}$  is the electron charge,  $m = 9.31 \times 10^{-31}$ kg is the electron mass,  $h = 6.626 \times 10^{-34} Js$  is plack constant,  $v_g$  is the memristor voltage,  $i_{(t)}$  current of the memristor,  $R_s$  is the electron resistance,  $v_R$  is the voltage accross the metallic channel series resistance,  $\phi_0$  is the effective barrier height, w is the barrier thickness(see figure 14) which is the state variable control. The model does not require a window function and it is assumed to be the most accurate physical model of the memristor for now. However, some of its limitation is that it is complicated in its mathematical rigor and expression; it does not provide explicit relationship between voltage and current; and may not be applicable to all types of memristor.

#### 3.5 ThrEshold Adaptive Memristor (TEAM) Model

TEAM model by Kvatinsky et al.[17] is a simple and general model that represents the Simmons Tunnel Barrier Model in a simpler expression.

$$\frac{dx_{(t)}}{dt} = K_{off} (\frac{i_t}{i_{off}} - 1)^{a_{off}} . F_{off}(x), \ 0 < i_{off} < i$$

(28)

$$\frac{dx_{(t)}}{dt} = K_{on} (\frac{i_t}{i_{on}} - 1)^{a_{on}} . F_{on}(x), \ i < i_{on} < 0$$

<sup>(29)</sup>

$$\frac{dx_{(t)}}{dt} = 0, \ i_{on} < i < i_{off}$$

(30)

where  $K_{off} > 0, K_{on} < 0, and K_{off}, K_{on}, a_{off}, a_{on}, i_{off}, i_{on}$ are constants where x is internal state variable; and  $F_{on}$  and  $F_{off}$  are window functions constraining x between the bounds  $x_{on}$  and  $x_{off}$ .

Thus, if the memristance changes linearly with the state variable, x, then we have that:

$$v_{(t)} = [R_{ON} + \frac{R_{OFF} - R_{ON}}{x_{off} - x_{on}} (x - x_{on})]i_{(t)}$$

(31)

Whereas, if the memristance changes exponentially with the width as in Simmons tunnel barrier, then we have that:

$$v_{(t)} = [R_{ON} exp \frac{\lambda}{x_{off} - x_{on}} (x - x_{on})]i_{(t)}$$

(32)

Where  $\lambda$  is the fitting parameter and  $R_{ON}$  and  $R_{OFF}$  are the effective resistances at the bound defined in terms of  $\lambda$  as follow:

$$\lambda = ln(\frac{R_{OFF}}{R_{on}}) \tag{33}$$

The TEAM model can be suitable for any memristor model. However, it made some assumptions which are as follows:

- (1) The sate variable is fixed below a certain threshold value.

- (2) A polynomial rather than exponential dependency exist between the current of memristor and the internal state drift derivative.

## 4. POTENTIAL APPLICATIONS OF MEMRISTOR

Memristor experimental manufacture by HP Lab as published in May 2008 [6] has since then sparked much interest and research in this newly fourth circuit element. Most importantly, the unique characteristics such as the memory property, nano scale dimension, high density memories, less power consumption and leakage current under parameter variations have made memristor a potential contender area of interest for researchers and promises to be the next generation memory de-facto standard for memory, logic, analogue and digital design. Therefore, the summary of its possible potential applications are as follows:

- —Artificial Neuromorphic Networks using memristive nanodevices and ultra dense non-volatile memories[9].

- —Memristive multi function logic design, content addresable memory, reconfigurable logic circuits, and combinatorial circuits [19].

- —Non Volatile memory design with Static Random Access Memory[3] and Memristive-Based Resistive Random Access Memory [20].

- -Reliable gas sensing with memristic crossbar array [18].

- ---Hybrid memristive-CMOS based computation-in-memroy architecture for high density computation.

- -Memristive-based Physical Unclonable Function.

- -Large storage with less energy consumption during switching to write or read the state of the switch.

- —Hybrid CMOS memristor circuits is applied in reconfigurable Boolean logic circuits such as field programmable gate arrays (FPGA)[9].

- —Ability to learn from its environment—mind of its own—hence for design of self reparable system.

- —The current memory challenge in "big data" can be resolved using memristor or memristive-CMOS hybrid architecture.

## 5. CONCLUSION

This paper clearly and succinctly presented the theory of memristor, the fourth circuit element with the mathematical models—linear, non lineear, exponential, Simmons Tunnel Barrier, and TEAM models including Biolek, Strukov, Prodromakis, Zha's window functions. There is collaborative need to explore through design and simulation this new circuit element that will usher in a new era of computation. Many industry giants and cutting-edge semi-conductor companies such as Hinix semiconductr inc., with IBM, and HP are currently having collaborative initiatives toward the fabrication and production of the memristor in large scale for building electronic and computing devices for neurocomputing, soft computing, big data applications, digital and analogue circuit design.

# 6. ACKNOWLEDGEMENTS

Major work in this paper is drawn from a chapter in the theses [3] submitted to University of Bristol. Thanks to Prof Dhiraj Pradhan and Dr Mathew Jimson who were motivators, inspiration and supervisors of the theses. Also, gratitude to Dr Adedotun Adeyemo and Engr Ndubuisi Ishiwu for corrections and criticism where necessary to produce a better piece of this paper.

## 7. REFERENCES

- [1] Chua, L.O., "Memristor- the missing circuit element", *IEEE Trans. Circuit Theory*, 1971,vol. CT-18, no. 5, p507 -519.

- [2] Chua, L.O. and Kang, S.M., "Memristive devices and Systems", *Proceedings of the IEEE 1976, vol. 64, no. 2, p209*-223.

- [3] Ezeogu, Apollos "Process Variation Aware Non- Volatile (Memristive) 9T SRAM Memory Design in Nano-CMOS Technologies", M.Sc. Theses submitted to University of Bristol, United Kingdom, Oct.2013

- [4] Kavehei, O.; Kim, Y.S; Igbal, A.; Eshraghian, K.; Al-Sarawi, S.F.; Abbott, D., "The Fourth Element: Characteristics, modeling, and Electromagnetic Theory of the memristor", In proceeding of: Communication, Circuits and systems, 2009. IC-CCAS 2009, International Conference on IEEE Xplore.

- [5] Chua Leon, "Everything You Wish to Know About Memristors But Are Afraid to Ask", *RADIOENGINEERING*, VOL. 24, NO. 2, JUNE 2015

- [6] Dmitri B. Strukov, G. S. Snider, Duncan. R. Stewart, R. Stanley Williams,"The missing memristor found," *Nature, vol.* 453, no. 179, pp. 80-83, May 2008.

- [7] Dmitri B. Strukov, Julien L. Borghetti, R. Stanley Williams, "Coupled Ionic and Electronic Transport Model of Thin-Film Semiconductor Memristive Behavior." *Small 2009. 5, no. 9.* 1058–1063.

- [8] http://spectrum.ieee.org/semiconductors/ processors/how-we-found-the-missing-memristor

- [9] Dmitri B. Strukov et al. "Hybrid CMOS/Memristor Circuits", Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium on May 30 2010-June 2 2010, pp. 1967 - 1970, Paris

- [10] Hyongsuk Kim, Maheshwar Pd. Sah, Changju Yang, Seongik Cho, and Leon O. Chua, "Memristor Emulator for Memristor Circuit Applications" *IEEE Transactions on Circuits and Systems–I: Regular Papers Vol. 59, No. 10, October 2012.*

- [11] Y.N. Joglekar and S.J. Wolf, "The elusive memristor: properties of basic electrical circuits," *Eur. J. Phys., vol. 30, pp.* 661-675, 2009.

- [12] Hazem Elgabra, Ilyas A.H. Farhat, Ahmed S. Al Hosani, Dirar Homouz, Baker Mohammad, "Mathematical Modeling of a Memristor Device" 2012 International Conference on Innovations in Information Technology (IIT), pp 156 - 161.

- [13] Zdenek Biolek, Dalibor Biolek, and Viera Biolkova, "SPICE Model of memristor with nonlinear dopant drift", *Radio En*gineering, Vol. 18, pp. 210-214, 2009 2009.

- [14] J. J. Yang, M. D. Pickett, X. M. Li, D. A. A. Ohlberg, D. R. Stewart, and R. S. Williams, "Memristive Switching Mechanism for Metal/Oxide/Metal Nanodevices," *Nature Nanotechnology, Vol. 3, pp. 429 - 433, Jul 2008.*

- [15] Themistoklis Prodromakis, Boon Pin Peh, Christos Papavassiliou, Christofer Toumazou," A Versatile Memristor Model With Nonlinear Dopant Kinetics", *IEEE Transaction on electronic Devices, Vol. 58, No. 9, September 2011.*

- [16] Pickett MD, Strukov DB, Borghetti JL, Yang JJ, Snider GS, Stewart DR, Williams RS. Switching dynamics in titanium dioxide memristive devices. *Journal of Applied Physics*. 2009;106(7):074508-6-074508-1. DOI: 10.1063/1.3236506

- [17] S, Kvatinsky, E.G. Friedman, A. Kolodny, and U. C. Weiser "TEAM: ThEshold Adaptive Memristor Model" *IEEE Transactions on Circuits and Systems 1: Regular Papers, vol.-, p.-,* 2012.

- [18] Adeyemo, A., Jabir, A., Mathew, J., Martinelli, E., Di Natale, C., and Ottavi, M. "Reliable gas sensing with memristive crossbar array" 23rd IEEE Int'l sympossium on IOLTS, Spain. http://dx.doi.org/10.1109/IOLTS.2017.8046228

- [19] Yang, X., Adeyemo, A., Bala, A. and Jabir A. "Novel Techniques for memristive multifunction logic design" *the VLSI Integration Journal, Spain. http://doi.org/10.1016/j.vlsi.2017.09.005*

- [20] Adeyemo Adedotun."Design of Reliable Memristive-Based Resistive RAMs (ReRAM)", M.Sc. Theses submitted to University of Bristol, United Kingdom, Sep. 2013

- [21] Zha J, Huang H, Liu Y. "A novel window function for memristor model with application in programming analog circuits" *IEEE Transactions On Circuits and Systems-II: Express Briefs.* 2016;63(5):423-427.DOI:0.1109/TCSII.2015.2505959