# **Behavior and Mathematical Modeling of PLL at 450MHz**

B. K. Mishra Principal Thakur college of Engg. & Tech. Kandivali (E), Mumbai-101 Sandhya Save Asst.Professor Thakur college of Engg. & Tech. Kandivali (E), Mumbai-101

Swapna Patil Asst.Professor Thakur college of Engg. & Tech. Kandivali (E), Mumbai-101

## ABSTRACT

Phase Lock Loop (PLL) is major analog circuit used for many different communication applications such as frequency synthesizer, radio, computer, clock generation and recovery, global positioning system etc. Therefore, the selection criteria for the desired PLL design is a critical and time consuming issue. This paper applies selection of proposed type of PLL for the desired application and analysis of third order PLL. The MATLAB Simulink tool is used for parameter selection and verification. The performance of PLL is tested and calculated for parameters like lock time, lock range, Bandwidth.

#### **General Terms**

Simulation, Design, Verification.

#### Keywords

CAD, EDA tools, Simulink VCO, PLL Baseband PLL, Charge pump PLL, literalized PLL

### **1. INTRODUCTION**

Phase locked loop is an excellent research topic as it covers many disciplines of electrical engineering such as Communication Theory, Control Theory, Signal Analysis, Noise Characterization, Design with transistors and op-Amps, Digital Circuit design and non-linear circuit analysis. Later on with the development of integrated circuits, it found uses in many other applications. The first PLL ICs came in existence around 1965, and was built using purely analog devices. Recent advances in integrated circuit design techniques have led to an increased use of the PLL as it has become more economical and reliable. Now a whole PLL circuit can be integrated as a part of a larger circuit on a single Chip i.e SoC[1] [13]. MATLAB simulink[15] is effective tool to get prior idea about PLL parameters to fulfill requirements before actual chip design. MATLAB simulink is effective tool to to get prior idea about PLL parameters to fulfill requirements before actual chip design.

Phase Locked Loops are used in almost every communication system. Some of its uses include recovering clock from digital data signals[3], performing frequency, phase modulation and demodulation, recovering the carrier from satellite transmission signals and as a frequency synthesizer[2]. There are many designs in communication that require frequency synthesizer to generate a range of frequencies; such as cordless telephones, mobile radios and other wireless products. The accuracy of the required frequencies is very important in these designs as the performance is based on this parameter [1] [13] [4].

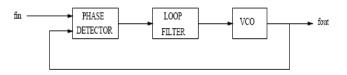

A Phase Locked Loop is a feedback control circuit. As the name suggests, the phase locked loop operates by trying to lock to the

phase of a very accurate input signal through the use of its negative feedback path. A basic form of a PLL consists of three fundamental functional blocks namely Phase Detector (PD), Loop Filter (LF), Voltage Controlled Oscillator (VCO). The block diagram of PLL is shown in the figure 1. The different types of PLL can broadly categories as Analog PLL, Digital PLL and Hybrid PLL.

#### Figure 1. The block diagram of PLL

PLLs have several unique characteristics when viewed from a control systems perspective. First of all their correct operation depends on the fact that they are nonlinear. The loop does not exist without the presence of two nonlinear devices, namely the phase-detector and VCO[3]. Therefore in this work the variation in different parameters for PLL are tested against VCO sensitivity, Loop filter transfer function for particular application.

The remainder of the paper is organized as follows. In Section 2, the basic of Linearized model of PLL is explained. The equation for lock time  $(T_L)$ , Bandwidth (BW) and lock range  $(\Delta w_L)$  is listed. In section 3,the frame for PLL design using Matlab/Simulink is explained. In section 4, the obtained results were compared with theoretical calculation.

### 2. LINEARIZED PHASE DOMAIN MODEL FOR PLL

The generalized loop response for the higher ordered PLL can be written as equation (1)[1], [2], [14]

$$\frac{\theta_0}{\theta_i} = \frac{K_p K_v F \ s}{s + K_n K_v F \ s} \tag{1}$$

Where,

$\theta_0$  = the output phase in radians

$\theta_i$  = the input phase in radians

$K_{\rm m}$  = the phase detector gain in volts per radian

$K_{v}$  = the VCO gain in radians per volt-second

$F_{s}$  = the loop filter transfer function (dimensionless)

The loop characteristics can be controlled by changing different types of loop filters then the order of PLL is  $_{n+1}$  where  $_n$  order of the loop filter.

The simplest filter is a one-pole RC circuit. The loop transfer function in this case is given a equation 2.

$$F \quad s = \frac{1}{1 + sRC} \dots (2)$$

The loop response for  $2^{nd}$  order PLL can be found out using eq. (2), (3).

$$\frac{\theta_0}{\theta_i} = \frac{\frac{K_p K_v}{RC}}{s^2 + \frac{s}{RC} + \frac{K_p K_v}{RC}}$$

(3)

Comparing the equation 3 with standard transfer function equation of second order filter we get,

$$\xi = \frac{1}{\sqrt{2}} \frac{1}{\sqrt{K_p K_v RC}}$$

(4)

$$\omega_n = \sqrt{\frac{K_p K_v K_v RC}{RC}}$$

(5)

Where,

RC=Time constant in sec.

$\xi$  = damping ratio

$\omega_{\rm w}$  = natural frequency

For sinusoidal phase detector  $K_P$  is  $^{1\!\!/}_2$  of peak to peak voltage of PD output [4]

Using equation (3),(4),(5) we get,

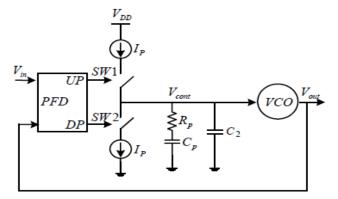

The corresponding values for lock time, Lock range, Bandwidth is calculated for different types of PLL, Baseband PLL, Charged Pump PLL[2]. The pump current  $I_p$  and selection of the capacitor C for filter design (mostly in nF) is an important design factor to be considered while designing charged pump PLL. Generally value of Ip is 100  $\mu A$  to 1 mA][2][7][4].

Equation(9),(10) obtained by comparing closed loop transfer function of second order PLL and standard second order PLL equation in terms of  $\omega_a, \xi$

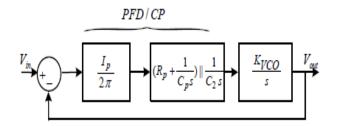

$$\omega_n = \sqrt{\frac{I_p K v co}{2 \Pi C_p}} \dots (9)$$

$$\xi = R_p \sqrt{\frac{I_p c_p K v co}{2 \Pi}} \dots (10)$$

As expected, if Rp=0, then  $\zeta$  =0. With complex poles, the decay time constant is given by equation (11) as

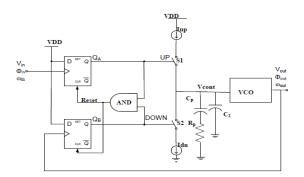

As seen from the closed loop transfer function of second order PLL equations (13), (14) if we decrease the  $I_p * K_{vco}$ , the gain crossover frequency decreases (or shifts toward the origin), degrading the phase margin. Since the charge pump drives the series combination of  $R_p$  and  $C_p$ , each time a current is injected into the loop filter, the control voltage experiences a large jump. Even in the locked condition, mismatches between  $I_{UP}$  and  $I_{DOWN}$  and the charge pump injection and clock feed through of S1 and S2 introduce voltage jump in  $V_{CONT}$  as shown in the figure 3.

Figure.2. Structure of third order charge pump PLL

Figure. 3. Addition of C2 to improve stability

Design and analysis of third order PLL is important as higher order design are concerns with system stability designed for wide applications.Trasfer function for second order filter for charge pump PLL is given by equation (12). The structure of third order charge pump PLL and System model of charge pump PLL block diagram shown in figure 2, figure 4 respectively.

Transfer function of loop filter is given by equation (12)

$Rp + 1/C_pS$  .....(12)

The open loop and closed loop transfer function is given by equations (12), (13).

$$G_{c}(s) = \frac{\frac{sI_{p}K_{vco}R}{2\Pi} + \frac{I_{p}K_{vco}}{2\Pi C_{1}}}{s^{3}mRC_{1} + \frac{sI_{p}K_{vco}R}{2\Pi} + \frac{I_{p}K_{vco}}{2\Pi C_{1}}}$$

(14)

where  $I_{p}$  is the current of charge pump,

$K_{vco}$  is the VCO gain constant

m=

$$\frac{c_2}{c_1}$$

is the capacitance ratio.

Usually, C2 is much smaller than C1 (m«1). Comparing equation (13) with equation (14) will get  $\xi$ ,  $\omega_n$  and m.

Figure 4.System model of charge pump PLL block diagram

#### 3. FRAME WORK FOR PLL DESIGN

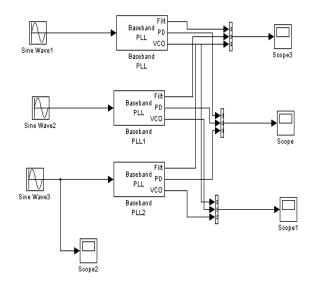

The set up arrangement done for PLL parameter measurement is shown in the figure 2. The similar set up is has been designed for Linearized Baseband PLL, Charged Pump PLL. The set up for Baseband PLL is shown in the figure 5.Similar set up is done for Linearized Baseband PLL, Charged Pump PLL.

#### 3.1 Setup for PLL Simulation in Simulink

The input provided in set up is order coefficient of Loop filter. For e.g., using the transfer function of Loop filter incorporated in automated program written in Matlab which guides to find the input to find the proper range of input applied to the set up assembly to get desired output. Similarly for other input parameters Like, VCO gain in Hz/volts and quiescent frequency were found out.

For analysis of third order PLL setup used is almost same as second order PLL, I/P for assemble are TF of loop filter, Kvco, quiescent frequency of VCO.

#### 3.2 Measurement of PLL parameters

The simulation is done in Simulink/Matlab 2009b on Intel processor core 2 Duo processor@ 2.93 GHz with 1.96GBRAM The simulated results for filter output ,phase detector output and VCO outputs can seen in real time using scope in Simulink.

# Figure 5. Setup for measurement of PLL parameters in Simulink

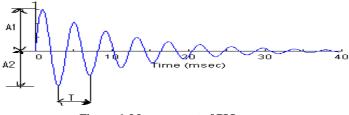

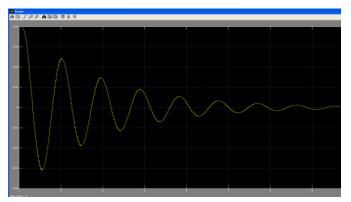

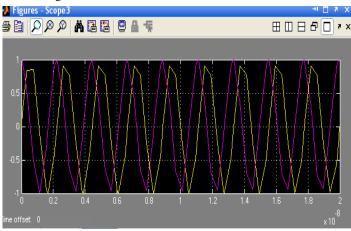

The obtained VCO output, filter output, Phase detector output for Charge pump PLL is shown in figure 7, figure 8 and figure 9 respectively.similarlly filter output (control signal),PD output and reference signal & VCO output shown in figure (10,11,12) respectively. These obtained data at least 5000 samples per result were stored in workspace. The peak value i. e A1 and next peak value A2 are found out from these samples using program

written in Matlab [9],[10]. Using these retrieved values  $\xi$  and  $\omega_n$

was found out using the formulae figure 6. [4]. The automated program files guides to find calculated and observed value for given RC time constant.

Figure 6. Measurement of PLL

Where,

A1=First maximum peak amplitude

A2 = First minimum peak amplitude

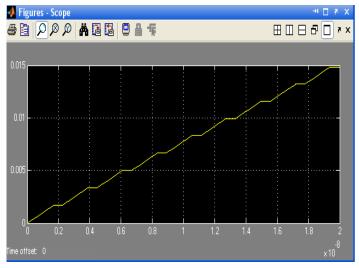

Figure 7. Charge pump PLL filter output

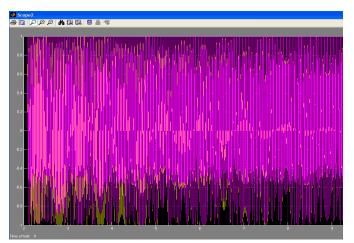

Figure 8. Charge pump PLL Phase detector output

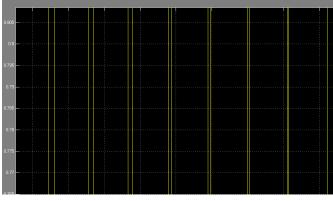

Figure 9. Charge pump PLL VCO output and input signal

Figure 10. Third order Charge pump PLL filter output

Figure 11. Third order Charge pump PLL Phase detector output

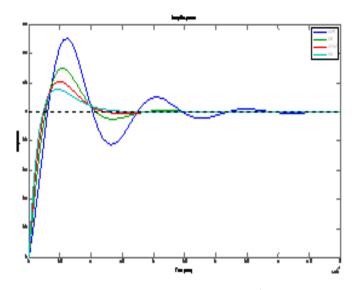

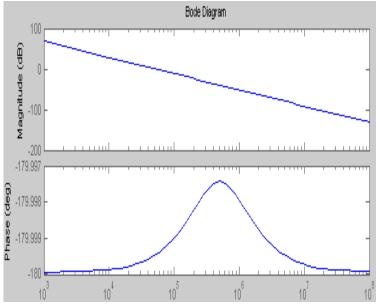

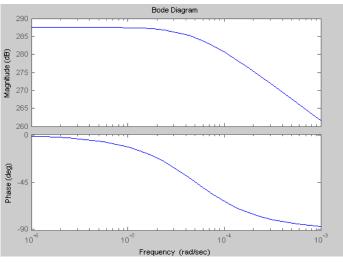

Output of PD and filter output indicate that  $\Delta \theta = 90$ . Bode plot of open loop and closed loop third order PLL shown in figure 14,15 respectively. The step response of third order system is shown in figure 13 shows.

# Figure 12. Third order Charge pump PLL VCO output and input signal

# 3.3 Automated program for third order Charge pump PLL

Automated program used for design of third order Charge pump PLL is written in MATLAB. These This program guides user to find the component values for specific parameter of PLL.

[cap res] = pll\_synth\_2nd\_order(ipump, vco\_sensitivity, fout, fcomp, bandwidth, pm)

Where,

ipump=chargr pump current

Kpd=(ipump/2)/pi; % phase detector gain

Kvco = vco\_sensitivity \*2\*pi; % vco gain

omega = 2\*pi\* bandwidth; % open loop bandwidth in radians/sec

Then after finding loop parameters using Ao,T1,T2 will get PLL design component values,Example is shown as following

example.

[cap res] =

pll\_synth\_2nd\_order(100e-6,166.948e6,450e6,100e3,200e6,60)

cap =

1.0e-016 \* 0.0630 0.8138 0 0 res = 1.0e+007 \* 3.6492 0 0

Figure 13. Step response for different values of <sup>*ξ*</sup> of Charge pump PLL

Figure 14. Open loop Bode plot of third order CPPLL

Figure 15. Closed loop Bode plot of third order CPPLL

# 4. RESULT AND DISSCUSSION

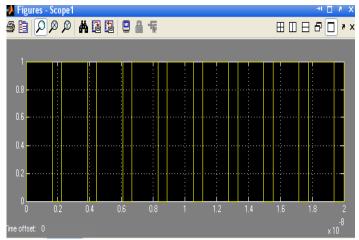

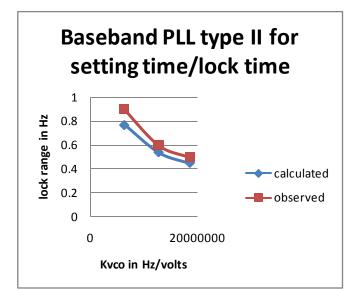

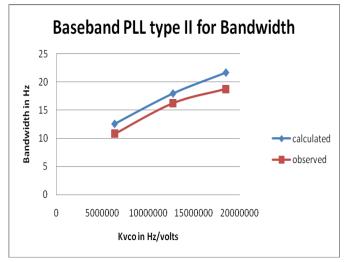

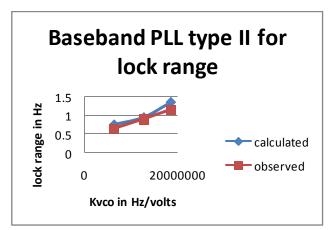

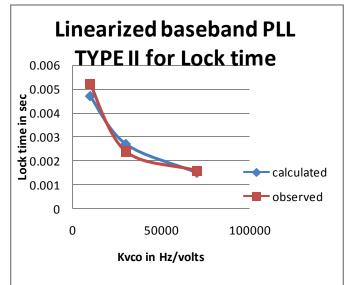

For the different type of PLL, the comparative study of obtained results of PLL for parameter such as setting time (sec to msec), Bandwidth (Hz to MHz),Lock range(Hz-KHz) is shown in figure 15-22.

Figure 15. Baseband PLL TYPE II for lock time

Figure 16. Baseband PLL TYPE II for Bandwidth

Figure 17. Baseband PLL TYPE II for lock range

From figure15-17, It can be found out that Baseband PLL can be used for narrow BW apllications such as GPS its around (0-10Hz) since the drawback is as Kvco increases setting time increases therefore selection RC time constant is acritical issue. and its lock range is small in range of few Hz.

Figure 18.Linearized Baseband PLL TYPE II for lock time

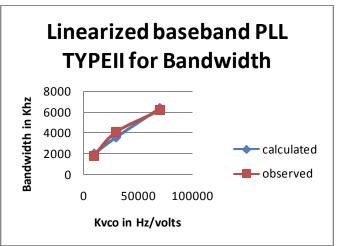

Figure 19.Linearized Baseband PLL TYPE II for Bandwidth

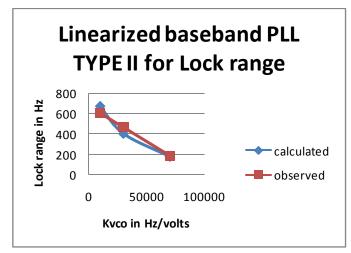

Figure 20.Linearized Baseband PLL TYPE II for lockrange

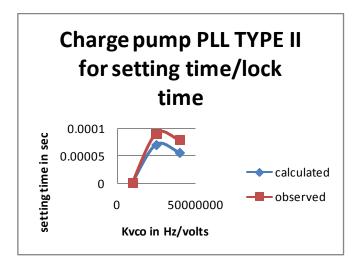

Figure 21.Charge pump PLL TYPE II for lock time

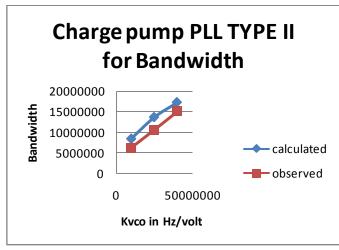

Figure 22. Charge pump PLL TYPE II for Bandwidth

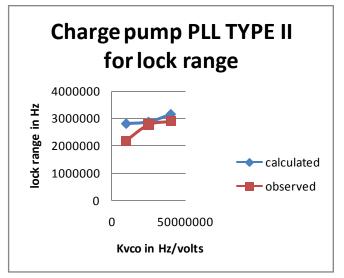

Figure 23.Charge pump PLL TYPE II for lock range

| Parameter     | $\xi = 0.707$ | $\xi = 0.9$ |

|---------------|---------------|-------------|

| Settling time | 125.7nsec     | 98.76nsec   |

| Overshoot%    | 1.18%         | 0.000035%   |

| m             | 0.000083      | 0.00001     |

| Loop gain     | 4.575Mhz      | 7.9056Ghz   |

From the graph 18-20, It was found that for Linearized PLL  $K_{VCO}$  inreases its lock range decreases drastically. The linearized model and the nonlinearized model differ in that the linearized model uses the approximation  $\sin(\Delta\theta(t)) \cong \Delta\theta(t)$  to simplify the computations. This approximation is close when  $\Delta\theta(t)$  is near zero. Thus, instead of using the input signal and the VCO output signal directly, the linearized PLL model uses only their phases.

From the graph 21-23, It was observed that for Charge pump PLL we get wider B andwidth [9], [11], [12], faster setting time and large lock range [13]. The comparative result table for baseband, Lineaized baseband and chgre pump PLL is listed in table 3.

#### Table 1.Simulation results for 0.707 and 0.9

Table 1 shows design of PLL at critical phase margin, and comparative effect for  $\xi = 0.707$  and  $\xi = 0.9$ . From the obtained results it can be seen that as damping factor increases the PLL setting time decreases ie faster setting ,as well as overshoot also decreases. Table 2 shows the list of componetnt valuecs obtained by using automated program.

#### Table 2. Design component values

| Damping factor | $C_1$  | $C_2$     | R            |

|----------------|--------|-----------|--------------|

| $\xi = 0.707$  | 0.1 µf | 83.03Pf   | 24k $\Omega$ |

| $\xi = 0.9$    | 2Pf    | 0.00002Pf | 20k $\Omega$ |

| PLL       | Kvco          | Lock time |         | Lock Range |       | Bandwidth  |            |

|-----------|---------------|-----------|---------|------------|-------|------------|------------|

| TYPE      | in<br>Hz/volt |           | Cal     | C          | al    | Cal        | obs        |

|           | s             | (         | Obs Obs |            |       |            |            |

| Baseband  |               | 0.75      | 0.0     | 0.75       | 0.65  | 12.5H      | 10.8H      |

| PLL       | 6.36          | sec       | 0.9     | 0.75       | 0.65  | 12.5H<br>Z | 10.8П<br>z |

| I LL      | KHz/v         | see       | sec     | Hz         | Hz    | L          | L          |

|           | olts          |           |         |            |       |            |            |

|           | 12.7          | 0.54      | 0.60    | 0.939      | 0.939 | 17.96      | 16.24      |

|           | k             | sec       | sec     | 3Hz        | 4Hz   | Hz         | Hz         |

|           | Hz/volt       |           |         |            |       |            |            |

|           | 8             |           |         |            |       |            |            |

|           | 18.5K         | 0.45      | 0.52    | 1.33       | 1.145 | 21.66      | 18.74      |

|           | Hz/volt       | sec       | sec     | Hz         | Hz    | Hz         | Hz         |

|           | s             |           | 300     | 112        |       |            | 112        |

| Charge    | 100           | 1.13      | 1.5µse  | 2.83       | 2.19  | 8.6        | 6.28       |

| pump      | Mhz/v         | µsec      | с       | MHz        | MHz   | MHz        | MHz        |

| PLL       | olts          |           |         |            |       |            |            |

|           | 250           | 70.4      | 90.5    | 2.89       | 2.78  | 138        | 152        |

|           | Mhz/v         | µsec      | usec    | MHz        | MHz   | MHz        | MHz        |

|           | olts          |           |         |            |       |            |            |

|           | 400           | 56.1      | 79.3    | 3.17       | 2.9   | 173        | 152        |

|           | Mhz/v         | µsec      | µsec    | MHz        | MHz   | MHz        | MHz        |

|           | olts          |           |         |            |       |            |            |

| Linearize | 10            | 4.7       | 5.2     | 671.2      | 601.9 | 2.039      | 1.8293     |

| d         | Khz/vo        | mse       | msec    | Hz         | 8Hz   | 7 KHz      | KHz        |

| baseband  | lts           | с         |         |            |       |            |            |

| PLL       | 30            | 2.7       | 2.4     | 405.2      | 464.9 | 3.592      | 4.119      |

|           | Khz/vo        | mse       | msec    | Hz         | 7Hz   | 2 KHz      | KHz        |

|           | lts           | с         |         |            |       |            |            |

|           | 70            | 1.5       | 1.6     | 186.0      | 182.0 | 6.349      | 6.213      |

|           | Khz/vo        | mse       | msec    | Hz         | 765H  | 3 KHz      | KHz        |

|           | lts           | с         |         |            | Z     |            |            |

|           |               |           |         |            |       |            |            |

Table 31. Comparative result table for all types of PLL

## 5. CONCULSION

The effect on parameters of second order PLL designed at 450M hz is discussed in this work. Simulation results show that  $\varepsilon$

and  $\mathcal{O}_n$  affect the behaviour of different PLL types. From the observed results, it is found out that, Linearized PLL is not used widely in communication applications due to constraint of smaller lock range for higher value of K<sub>VCO</sub>. The use Baseband PLL is restricted to for narrow BW apllications such as GPS systems in mobile communication whereas, Charge pump PLLcan be widely used for many communication application due to its advantage as it provides wider Bandwidth, less setting time and wider lock range.

The novel method for analysis and simulation of third order PLL is proposed. This method is an efficient method which helps to find stability of system with good precision in designed parameters. In future, we proposed to analysis of PLL in presence of noise and to achieve minimum phase noise.

#### 6. **REFERENCES**

- A. B. Grebene, *The monolithic phase-locked loop a versatile building block*, IEEE Spectrum, vol. 8, pp.38-49, March 1971.

- [2] B. Razavi (ed.), *Monolithic Phase-Locked Loops and Clock Recovery Circuits*, IEEE 2003.

- [3] Gursharan Reehal, A Digital Frequency Synthesizer Using Phase Locked Loop Technique" 1998

- [4] F. M. Gardner, *Charge-Pump Phase-Lock Loops*, IEEE Trans. On Communications, vol. 28, pp. 1849-1858, November 1980.

- [5] F.M Gardner, *Phase lock Techniques*, 2nd ed., John-Wiley & Sons, Inc., NY, 1979.

- [6] K. H. Cheng, W. B. Yang, and C. M. Ying A dual-slope phase frequency detector and charge pump architecture to achieve fast locking of phase-locked loop, IEEE Trans. Circuit and System II, vol. 50, pp. 892-896, Nov. 2003.

- [7] Liu yu-zhen, Design of phase-Locked loop based on SIMULINK, Liaoning Technical University's Transaction,vo. 23, no. 2, pp. 236–237, 2004.

- [8] L. C. Liu and B. H. Li, *Fast locking scheme for PLL frequency synthesiser* Electronics Letters, vol. 40, pp. 918-920, July 2004

- [9] P.E. Allen ,*PLL Design Equations & PLL Measurement*" ECE 6440 - Frequency Synthesizers

- [10] R. E. Best, Phase-Locked Loops: Theory, Design and Applications. New York McGraw-Hill, 1984

- [11] R.E. Best, *Phase-Locked Loops: Design, Simulation, and Applications,* 4th edition, McGraw-Hill, 1999 (4th edition)

- [12] JT. A. Telba and Abdulhameed Al-MazrooA, Wideband Low Jitter Frequency Synthesizer Modeling and Simulation, IJCSNS International Journal of Computer Science and Network Security, VOL.10 No.1, January 2010

- [13] J Ms. Ujwala A. Belorkar and Dr. S.A.Ladhake ,Dssign of loe power phase Locked Loop (PLL) using 45NM VLSI TECHNOLOGY,International journal of VLSI design & Communication Systems (LSICS), Vol.1, No.2, June 2010

- [14] F. You, and S. He, "Analysis of Third-order Charge Pump PLLs,"IEEE conf., 2004, pp. 1372-1376

- [15] A.Carlosena, A.M. Lazaro, "A Novel Design Method for Phased-Locked Loops of any Order and Type," IEEE conf., 2006, pp. 569-573.

- [16] Yunfei Ye ,Ming Zhang "Analysis and Simulation Three Order Charge Pump Phase Locked Loop" 978-1-4244-2108-4/08/\$25.00 © 2008 IEEE.