# A Fuzzy based DSP Implementation for Power Quality Improvement of a three phase AC-AC Converter

N.Radhakrishnan Lecturer Department of Electrical Engineering, Annamalai University, Annamalai nagar, TamilNadu-608002

## **ABSTRACT:**

This paper proposes the use of a fuzzy logic controller (FLC) that serves to enhance the power quality of a three phase ac-ac converter system with a dc link. The FLC is designed so as to shape the load current to a nearly sinusoidal fashion and contribute in improving the input power factor, lowering the total harmonic distortion (THD) and eliminating higher order harmonics. The Digital Signal Processor (DSP), besides generating the PWM gating pulses for the power switches, is programmed to function as PI/FUZZY controller in the feedback loop. The algorithm allows the modulation index to vary, in order to regulate the load voltage. Simulation and experimental results are included to highlight the fact that the scheme also enables to maintain a constant output voltage over a wide range of load variations,

# **KEYWORDS:**

Power quality, PWM inverter, DSP, Voltage regulation.

# **INTRODUCTION**

PWM voltage source inverters (VSIs) transform frequency and amplitude of ac voltage according to the system requirements. Most of them employ carrier based PWM (CBPWM) methods due to their fixed switching frequency, low ripple current, and well-defined harmonic spectrum characteristics. The significant advantage is that they serve to provide a linear relationship between the reference and output voltages within a limited range. The linear voltage range of a PWM-VSI is mainly determined by the modulator characteristics.

The PWM VSIs are required to maintain a sinusoidal output waveform for various types of loads, in addition to offering acceptable standards of power quality. A number of closed loop control schemes for PWM inverters with instantaneous feedback, by using analog techniques have been realized to achieve good dynamic performance and low total harmonic distortion (THD) [1,2]. The instantaneous feedback control with adaptive hysteresis has served to regulate the PWM inverters with direct current and voltage

feedback [3,4]. The hysteresis width has been made to change as a function of the voltage reference.

However its dynamic response to large change in loads has not been fully analyzed. With rapid progress in microelectronics technology, digital control of inverters using advanced Microcontrollers and Digital Signal Processors has gained significance [5,6]. Microprocessor based deadbeat control M.Ramaswamy Professor Department of Electrical Engineering, Annamalai University, Annamalai nagar, TamilNadu-608002.

technique has been applied to closed loop regulation of PWM regulation for UPS applications [7,8]. Very recently Discrete Sliding Mode Control (DSMC) approach has been used for the regulation of PWM inverters [9]. The main advantage of the DSMC scheme is its insensitivity to parameter variations and load disturbances, which leads to time invariant steady state response in the ideal case. Its disadvantages are it is not easy to find an appropriate sliding surface and its performance will be degraded with a limited sampling rate. A true sine single phase PWM inverter has been realized through a single chip DSP [10]. The algorithm, built in it, has served to achieve a fast control of the current in the PWM inverter. A simplified control strategy has been used **to** achieve enhanced power quality in a dc-ac system using the dc link series resonant based inverter [11].

When a VSI is fed by a fluctuating dc link voltage, it generates additional sub-harmonics that results from the modulation between the inverter switching function and the dc link ripple. Moreover, the ripple in the dc link is the primary contributor for the appearance of harmonics in the inverter output not present in the PWM switching function and is responsible for the deterioration in the quality of the output voltage. Further the harsh loads on the inverter power supply contribute to waveform distortion and introduce abnormal harmonics in the inverter input current. The switching action further creates ripples at the dc-link level. The input voltage distortion in a voltage source PWM controlled inverter will limit the amplitude of the fundamental and introduces unexpected lower order harmonics components. The use of conventional harmonic reduction techniques ends up only with the reappearance of the lower order harmonics in the output waveform. It is only appropriate that the next generation PWM modulators for inverters be inherently capable of rejecting the dc-link voltage ripple to offer a higher quality of output voltage.

# PROPOSED

# STRATEGY

The objective is to build a novel voltage regulation scheme for a three phase VSI, which will serve to offer an improved performance compared to existing methods in terms of minimal lower order harmonics, reduced THD, and enhanced fundamental, especially at low switching frequency.

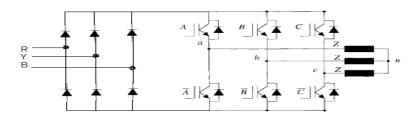

Fig.1 Power circuit

The power circuit, consisting of a front end rectifier in cascade with a three phase full bridge inverter as seen in Fig.1 is designed to feed power to a three phase resistive load. The controller in the feedback path derives its inputs from (i) the input ac signal transformed through a dqo block and (ii) a voltage per unit reference. It attempts to correct the error generated because of the deviation of the output voltage away from the reference value. The process serves to compute the modulation index, which in turn offers a change in the control voltage in order to activate the PWM generator.

use of linguistic variables rather than numerical values to

The underlying strength of fuzzy logic is that it makes

**FUZZY ALGORITHM**

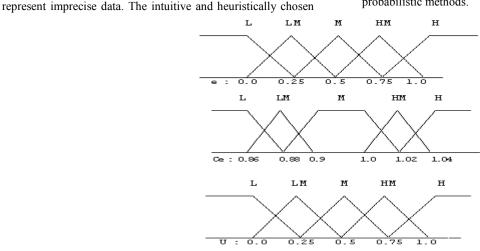

input linguistic variables are 'e', the voltage error and 'ce', the change in error; and the output linguistic variable is 'u', the current reference.

The fuzzy terms describing the identified variables are low (L), low-medium (LM), medium (M), high-medium (HM) and high (H). The sets defining the e, ce and u are as follows:

A one-dimensional triangular membership function with the range of values as shown in Fig.2 is chosen for input and output linguistic variables. The construction of membership functions can be based on intuition, rank ordering or by using probabilistic methods.

Fig.2 Membership function chosen for linguistic variables

The FLC is designed to calculate the current reference for the controller. The two inputs to the fuzzy algorithm are (i) the error (e) between a reference voltage and the actual load voltage, which droops because of the increase in current, and (ii) the change in error (ce) which is precisely the difference between the error at a certain operating point and the preceding error. The rules are summarised in the fuzzy decision matrix in Table 1. The consequents of the rules are shown in the shaded part of the matrix. The fuzzy results must be defuzzified through what is called a defuzzification process, to achieve a crisp numerical value. The most commonly used centroid or centre of gravity defuzzification strategy is adopted.

| Γ | AND |    | CE |    |    |    |    |  |  |  |

|---|-----|----|----|----|----|----|----|--|--|--|

|   |     |    | L  | LM | Μ  | HM | Η  |  |  |  |

|   |     | L  | LM | LM | L  | L  | L  |  |  |  |

|   |     | LM | M  | LM | LM | L  | L  |  |  |  |

|   |     | Μ  | Μ  | Μ  | LM | LM | L  |  |  |  |

| E | Ξ   | Н  | HM | Μ  | Μ  | LM | LM |  |  |  |

|   |     | Н  | Η  | HM | Μ  | M  | LM |  |  |  |

**Table 1 Fuzzy Decision Matrix**

The current reference thus determined is compared with the input current in a controller which in turn serves to generate the pulses for the three MOSFET switches in the three phase ac-dc converter.

# SIMULATION

changes in supply and load are introduced independently and the results obtained. The scheme is simulated using MATLAB-Load current 'ab Loac 0.08 0.1 0.06 0.120.1 0.04

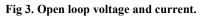

It is observed from the open loop performance in Fig 2 that when a step change in load is introduced at 0.04sec, the load current increases. It is accompanied by a decline in load voltage.

Further when a step change in the source voltage is created at 0.08sec, the load voltage increases and settles rapidly at a new value.

SIMULINK. The performance of the schematic is tabulated for a

range of load powers allowed to vary from 2 to 5 KW. The load voltage, load current and input dc voltage corresponding to a

load of 4KW is depicted in Figs 3 and 4. The frequency

spectrum for the same operating state is displayed in Fig. 5. Step

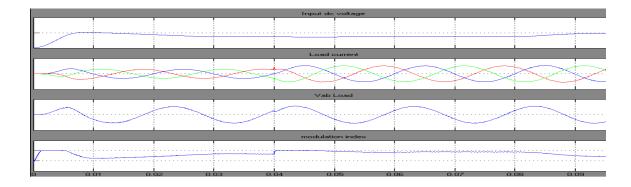

Fig 4.Closed loop voltage and current.

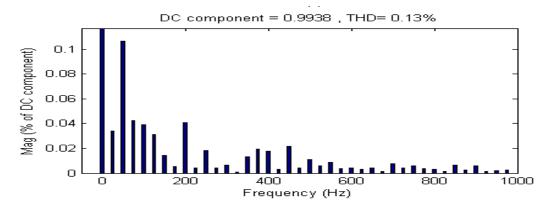

#### Fig 5. Frequency spectrum.

When a load disturbance occurs at 0.04sec, the load current increases as seen in Fig. 4. Though the load voltage attempts to decline, it is almost instantaneously corrected by the action of controller in the feedback path. It is followed by an increase in

the modulation index. A similar effect is observed at 0.08sec when a sudden change occurs in the supply. The modulation index decreases and serves to maintain the voltage at the same

| Load<br>( KW) | Load voltage (Volts)               |                | Load              | Input power factor |             | Modulation    | THD in %  |                |

|---------------|------------------------------------|----------------|-------------------|--------------------|-------------|---------------|-----------|----------------|

|               | Open loop<br>(with $m_a = 0.817$ ) | Closed<br>loop | current<br>(Amps) | Open loop          | Closed loop | index<br>(Ma) | Open loop | Closed<br>loop |

| 2             | 239.4                              | 230.3          | 8.6               | 0.9714             | 0.9787      | 0.7899        | 0.40      | 0.26           |

| 2.5           | 234.5                              | 230.3          | 10.8              | 0.9685             | 0.9774      | 0.8033        | 0.36      | 0.24           |

| 3             | 229.3                              | 230.2          | 12.8              | 0.9656             | 0.9762      | 0.8177        | 0.32      | 0.20           |

| 3.5           | 223.9                              | 230.3          | 15.0              | 0.9629             | 0.9749      | 0.8344        | 0.30      | 0.17           |

| 4             | 218.3                              | 230.4          | 17.2              | 0.9604             | 0.9735      | 0.8525        | 0.28      | 0.16           |

| 4.5           | 212.6                              | 230.3          | 19.3              | 0.9581             | 0.9725      | 0.8728        | 0.26      | 0.15           |

| 5             | 216.7                              | 230.2          | 21.4              | 0.9561             | 0.9716      | 0.8930        | 0.24      | 0.15           |

Table 2. Open and closed loop performance

value. The results highlight the usefulness of the controller in the feedback path, in the sense the overall power quality is considerably improved.

#### HARDWARE IMPLEMENTATION

The distorted dc obtained through the front end rectifier serves as a source of input to the inverter module. The signal conditioned feedback signal is compared with set point value to determine the error. The error and change in error are processed in order to enable the DSP, programmed to function as a PI/FUZZY controller, to generate a new value of modulation index for the PWM signals that are applied to the gate of MOSFET through an isolator and a driver.

The Texas Instruments TMS320LF2407A DSP combines the powerful CPU with on chip memory and peripherals. With the core and control oriented peripherals integrated in a single chip, the user is offered the ease-of-use

facility over a traditional micro controller and higher processing power. Besides it is very compact and cost effective.

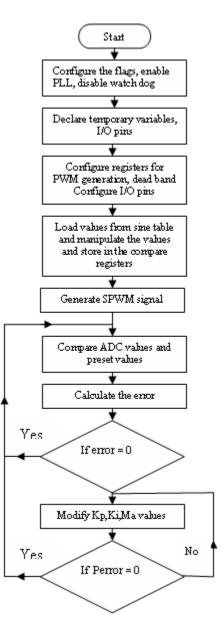

The core, a 16 bit fixed point processor has its own native instruction set and can be programmed either in assembly or C language. The architecture, Harvard-Style in structure consists of three execution units operating in parallel and allows as many as six operations per instruction cycle. The event manager, one of the most important peripherals, is made up of EVA and EVB. Each EV is composed of functional blocks that facilitate PWM generation. The power switches in the inverter is driven by PWM signals generated using the DSP. The firing signals are obtained through a sine reference-triangular carrier modulation procedure inside the discrete PWM generator. The flowchart of the DSP based algorithm is shown in Fig. 6.

#### **INTERPRETATION**

The prototype built shown in Fig. 7 is tested for the same range of load powers and the results are tabulated in Table 3. The DS2407 processor in the feedback path serves to

calculate the gains for the PI controller, with the objective to regulate the output voltage, besides improving the power quality. The steady state voltage and current waveforms corresponding to a load power of 4 KW is displayed in Figs. 8 10.

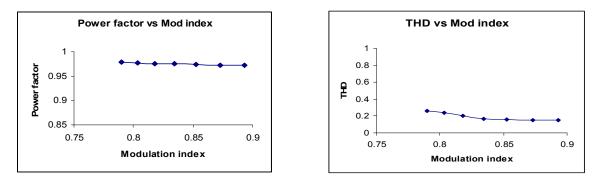

and 9. The performance of the model obtained with a 10% change in load is seen in Table 4. The variation of input power factor and THD with modulation index is plotted in Fig.

©2010 International Journal of Computer Applications (0975 - 8887) Volume 1 - No. 24

Fig.7. Experimental setup

Fig.8.Steady state voltage wave form

### Table 3. Comparison of simulation and hardware results

| Load<br>(KW) | Load voltage<br>(Volts) |          | Load current<br>(Amps) |          | Input power factor |          | Modulation index<br>(Ma) |          |

|--------------|-------------------------|----------|------------------------|----------|--------------------|----------|--------------------------|----------|

|              | Simulation              | Hardware | Simulation             | Hardware | Simulation         | Hardware | Simulation               | Hardware |

| 2            | 230.3                   | 230.5    | 8.6                    | 8        | 0.9787             | 0.9686   | 0.7899                   | 0.8000   |

| 2.5          | 230.3                   | 230.3    | 10.8                   | 9.5      | 0.9774             | 0.9675   | 0.8033                   | 0.8090   |

| 3            | 230.2                   | 230.3    | 12.8                   | 12       | 0.9762             | 0.9658   | 0.8177                   | 0.8200   |

| 3.5          | 230.3                   | 230.2    | 15.0                   | 14.5     | 0.9749             | 0.9630   | 0.8344                   | 0.8442   |

| 4            | 230.4                   | 230.1    | 17.2                   | 17.5     | 0.9735             | 0.9629   | 0.8525                   | 0.8500   |

| 4.5          | 230.3                   | 229.8    | 19.3                   | 20       | 0.9725             | 0.9617   | 0.8728                   | 0.8701   |

| 5            | 230.2                   | 229.2    | 21.4                   | 22       | 0.9716             | 0.9609   | 0.8930                   | 0.8900   |

## Table 4. Comparison of simulation and hardware results with load and source disturbances

|                         | Time<br>(Secs) | Ma     |       | V <sub>L</sub> (Volts) |       |       |

|-------------------------|----------------|--------|-------|------------------------|-------|-------|

|                         |                | Before | After | Before                 | After |       |

| (10%)Source disturbance | Simulation     | 0.08   | 0.897 | 0.811                  | 230.4 | 230.3 |

| ()                      | Hardware       | 0.08   | 0.88  | 0.8                    | 230.1 | 230.5 |

| (10%) Load disturbance  | Simulation     | 0.04   | 0.893 | 0.9161                 | 230.2 | 229.9 |

| (,                      | Hardware       | 0.04   | 0.88  | 0.9                    | 230.5 | 229.2 |

Fig.9.Steady state current wave form

Fig.10.Variation of input power factor and THD with Modulation index

# CONCLUSION

A novel closed loop scheme has been built in the feedback path through the use of a PI controller. The DSP programmed to perform the PI action has served to maintain the inverter output voltage constant over a wide range of load variations. The simulation and experimental results display the capability of the inverter to handle transient disturbances and claims its use in sophisticated applications such as UPS. Their close comparison highlight the merits of this scheme and points out that it can easily be extended to meet the needs of other applications such as variable speed drives.

# **REFERENCES:**

[1] A.Kernick, D.L.Stechschulte, and D.W.Shireman, "Static inverter with synchronous output waveform synchronized by time-optimal response feedback," *IEEE trans. on IECL*, vol. 24, no. 4, pp. 197-305, 1977.

[2] Y.Sekino, M.Shibata, and N.Hotaka, "Inverter output voltage waveform closed-loop control technique," *INTELEC Tokyo*, pp. 205-212.Oct. 1983.

[3] A.Kawamura, R.Hoft, "Instantaneous feedback controlled PWM inverter with

adaptive hysteresis," *IEEE trans. on Ind. Appli.*, vol. 20, no. 4, pp. 769-775, 1984.

[4] M.Carpita, M.Mazzucchelli, S.Savio, and G.Sciutto, "A new PWM control system for UPS using hysteresis comparator," *IEEE CH2499-2*, pp. 749-754, 1987.

[5] B.K.Bose, Editor, *Microcomputer Control of Power Electronics and Drives, IEEE Press.* 1987.

[6] Y.Dote, Servo Motor and Motion Control Using Digital Signal Processors, Prentice Hall and Texas Instruments Digital Signal Processing Series, 1980.

[7] Han-Ju Cha, et al, "Real-time digital control of PWM inverter with PI compensator for uninterruptible power supply," *Int. Conf. Ind. Electronics Contr. and Inst.*, vol. 2, pp. 1125-1128, 1990.

[8] C.Hua, and R.G.Hoft, "High performance deadbeat controlled PWM inverter using a current source compensator for nonlinear loads," *IEEE Power Electron. Speacialists' ConfRec.*, pp. 443-450, 1992.

[9] S.L.Jung and Y.Y.Tzou, "Sliding mode control of a closedloop regulated PWM Inverter under large load variations," *IEEE Power Electron. Speacialists' ConfRec.*, June 1993.

[10] Ovidiu Pop, Gabriel Chindris, Andrei Dulf, "Using DSP technology for true sine PWM generators for power inverters", *IEEE 27<sup>th</sup> Int'l spring seminar on electronics technology*, pp.141-146, 2004.

[11] A.Muthuramalingam, S.V.Vedula and P.A.Janakiraman, "Performance evaluation of an FPGA controlled soft switched inverter", *IEEE trans. on Power Electronics*, vol.21, no.4, pp.923-932, July 2006.

## ACKNOWLEDGEMENT

The authors thank the authorities of Annamalai University for the facilities provided.