# Improving Error Correction Capability of Aggressive Packet Combining Scheme by using Half-Byte Packet Reverse Technique and Even - Odd Selection Method

Yaka Bulo

National Institute of

Technology

Yupia, PapumPare District,

Arunachal Pradesh

Preeti Sharma

National Institute of

Technology

Yupia, PapumPare District,

Arunachal Pradesh

C.T. Bhunia

National Institute of

Technology

Yupia, PapumPare District,

Arunachal Pradesh

## ABSTRACT

Aggressive Packet combining scheme is very efficient technique for error correction in wireless data communication. Transmitter transmits three copies of the original packet. Receiver applies bit by bit majority voting on the received erroneous copies and gets the original packet.

The major limitation of APC is that, if the bit error occurs in the same bit location of all the received copies then APC fail to correct them which results in reduced correction capability and reduced throughput. In this paper, a new modified APC technique is proposed that can eliminate the major limitation of the APC by using half-byte packet reverse technique and even & odd selection method thus increasing correction capability and throughput.

## General Terms

Correction capability, odd-even selection, packet reverse technique.

## Keywords

Aggressive packet combining (APC), bit wise majority logic, packet reverse packet combining scheme, even & odd selection.

## 1. INTRODUCTION

A major challenge faced by the researcher is to transmit the data from transmitter to receiver successfully. Practically the channels are not stable all the time thus, erroneous packet are received at receiver side. Two techniques i.e. Forward Error Correction (FEC) and backward error correction are used for reliably transferring data from sender to receiver. In BEC retransmission technique is used for error correction thus, transmission delay occurs. Backward error correction is suitable for the wired transmission. Forward error correction is suitable for the wireless communication where error correction codes are used for detection and correction of error if any. Leung [1] proposed an idea of Aggressive Packet Combining scheme (APC) for error control in wireless networks with the basic objective of fast error control in relatively higher noisy wireless networks. In APC, three copies of a packet is transmitted from source node to destination node. If all the received copies are erroneous, bit by bit majority voting is applied to get the correct packet. A major drawback of APC is that if error occurs in same location of erroneous copies of a packet then the application of majority logic fails to get original packet. Several modifications of APC are reported in [2-8] to increase throughput, tackling various error syndromes and enhancing fast correction.

In this paper, the modified APC technique is proposed to overcome the problem of conventional APC (if the error occur in same bit location of all the received copies, then APC fail to correct them) by using half-byte packet reverse at 2<sup>nd</sup> copy and even /odd selection method at 3<sup>rd</sup> copy. Theoretical analysis shows that the proposed scheme has better error correction capability than the conventional APC.

## 2. REVIEW OF HALF-BYTE PACKET REVERSE SCHEME AND APC

### 2.1. Half-Byte Packet Reverse Scheme

The idea behind Half-Byte packet reverse scheme was taken from Packet Reverse Packet Combining scheme (PRPC) [9-10]. In this scheme, each half-byte of packet is separately reversed and combined and then transmitted. Receiver side applies the same phenomena to decode the received packet. Let us understand this by considering an example:

Let the original packet is 10101100

Transmitter:

Table 1. Half-Byte Reverse at Transmitter

|                                 |      |

|---------------------------------|------|

| First half byte reverse=1010    | 0101 |

| Second half byte reverse = 1100 | 0011 |

Transmitter transmits: 01010011

Receiver side: Erroneous copy as 01011011 (Bold face shows error bit) and applying reverse phenomena we get as table 2.

Table 2. Half-Byte Reverse at Receiver

|                          |      |

|--------------------------|------|

| First half byte reverse  | 1010 |

| Second half byte reverse | 1101 |

Now receiver has **10101100** and is the original packet.

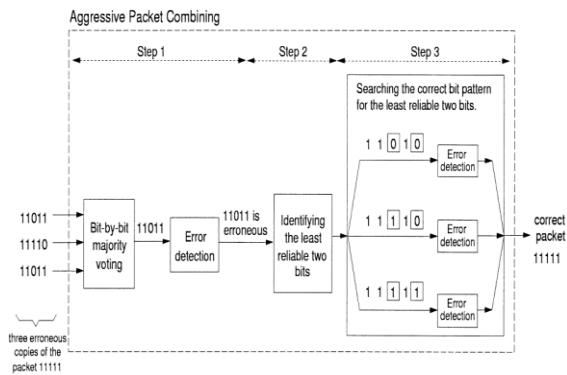

### 2.2 Aggressive Packet combining scheme

Aggressive packet combining scheme is a modification of MjPc (Majority Packet Combining) [11]. In APC three copies of the original packet is send from source to destination. If received copies are erroneous then bit-by-bit majority logic is applied on the three copies at receiver side and combined

packet is again applied to error detection test. If it is found to be erroneous then least reliable bits are identified. And correct bit pattern for these bits are again searched. All the generated copies are again applied for error detection and if correct packet is obtained then next packet is requested, if not correct then retransmission is requested for same packet. Figure 1 shows an example.

**Fig. 1: Aggressive Packet Combining Scheme.**

APC fails when error occurs at same bit location in all the copies as in example 3 where error locations are shown in bold face.

**Table 4. APC scheme when error is at same location in three copies of 10101 packet (red colored is erroneous bits).**

| Received Copies | Bit-by-Bit Majority Logic | Error Detected | Least Reliable bits                                | Search the Correct Pattern | Error Detected |

|-----------------|---------------------------|----------------|----------------------------------------------------|----------------------------|----------------|

| 11111           |                           |                |                                                    | 11111                      | Yes            |

| 11101           | 11101                     | Yes            | 1 <sup>st</sup> and 2 <sup>nd</sup> bit from right | 11110                      | Yes            |

| 11100           |                           |                |                                                    | 11100                      | Yes            |

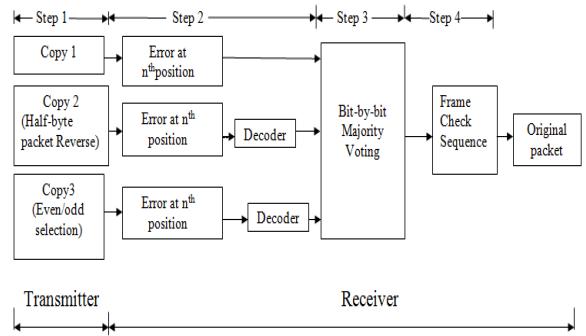

### 3. PROPOSED SCHEME

As it is likely in wireless transmission that three copies transmitted at a time will have the same link error syndrome resulting into all three copies having error at same bit position(s) [12-13]. In order to overcome the drawback (i.e. correction of error when error occurs at same bit location of two or more copies) of conventional APC, new modified technique of APC is introduced for transmission of packet from source to destination. In this modified technique, if the two or more error occurs in the same bit location, then it can be detected and corrected to get the original copy by applying half-byte packet reverse and even & odd selection method. The idea is based on the logic that bit reversal or positional changes in the transmitted copies may reduce the occurrence of double or triple bit error in same location after decoding at the receiver using same logic thus increasing the correction capability. Figure 2 shows the diagram of the proposed scheme and it can be understood as per the diagram in figure 2.

**Fig. 2: Proposed Scheme**

The main idea of the proposed scheme can be explained by executing the following steps:

#### At transmitter

##### Step 1:

- Copy 1 of the original packet is transmitted without any coding.

- Copy 2 is transmitted after applying half-byte packet reverse logic of packet. In this logic packet is divided into two halves and then packet reverse is applied on the two halves and then combined as a single packet and then transmit it to the receiver. It is illustrated as the original packet is 10100101.

1010 0101

↓ ↓

0101 1010

Transmitted copy is 01011010.

- Copy 3 is transmitted after applying odd and even selection method where even bits are placed in left side and odd bits are placed in right side of the packet.

#### At receiver

##### Step 2:

- Error detection of each copy takes place to detect the presence of errors at the received copies.

- Error detection is followed by decoding of second and third copies.

##### Step 3:

- Bit-by-bit majority voting is applied on the decoded copy 2, copy 3 and copy 1.

##### Step 4:

- Copy obtained after step 3 is again applied to the error detection (FCS) to find whether the obtained copy is erroneous or not. If no error is detected then we get the original packet and if error is detected then copies are discarded and request for retransmission of the packet.

Let us understand the scheme considering various examples as follows:

Example 1: Say the original copy is 10100101.

- First copy,  $C_O = 10100101$ , it is received with error in 2<sup>nd</sup> position from left as  $C'_O = 11100101$

- Second Copy with Half-byte packet reverse,  $C_{HPR} = 01011010$ . It is received with error in the same bit position as that of the first copy as  $C'_{HPR} = 00011010$ . Receiver decode the received copy using the same logic and get the copy as  $C'_{HPR} = 10000101$ .

- Third copy with even-odd bit selection,  $C_{EO} = 00111100$  (blue colored are even bits and black colored bits are odd). It is again received with error at same position i.e. 2<sup>nd</sup> bit from left side as  $C'_{EO} = 00111100$ . Receiver decode the copy using same logic and get the copy as  $C'_{EO} = 10100101$ .

- Apply bit-by-bit majority voting on all the three copies and get the result. Apply error detection on the obtained copy to find whether obtained copy is correct or not. If correct, next packet is requested. If not, retransmission is sought. Whole procedure is presented in tabular form:

Example 2: Original packet is 10100101

**Table 5. Proposed scheme for the packet 10100101**

| Transmitter                                       | Receiver      |               |                           |                 |

|---------------------------------------------------|---------------|---------------|---------------------------|-----------------|

|                                                   | Received Copy | Decoded copy  | Bit-by-Bit Majority logic | Error Detection |

| $C_O: 10100101$                                   | 11100101<br>1 | 11100101<br>1 |                           |                 |

| $C_{HPR}: 01011010$<br>(Half-Byte Packet Reverse) | 00011010<br>0 | 10000101<br>1 |                           |                 |

| $C_{EO}: 00111100$<br>(Even-odd selection)        | 00111100<br>0 | 10110101<br>1 |                           |                 |

Example 3: Original packet is 00101010

**Table 6. Proposed scheme for the packet 00101010**

| Transmitter    | Receiver      |               |                           |                 |

|----------------|---------------|---------------|---------------------------|-----------------|

|                | Received Copy | Decoded copy  | Bit-by-Bit Majority logic | Error Detection |

| $C1: 00101010$ | 00111010<br>0 | 00111010<br>1 |                           |                 |

|                                               |          |          |  |                                  |

|-----------------------------------------------|----------|----------|--|----------------------------------|

| C2:<br>01010101<br>(Half-Byte Packet Reverse) | 01010101 | 10101010 |  | No<br>(00101010 = Original copy) |

| C3:<br>00000111<br>(Even-odd selection)       | 00010111 | 00101011 |  |                                  |

Example 4: Original packet is 11011011.

**Table 7. Proposed scheme for the packet 11011011**

| Transmitter                                   | Receiver      |              |                           |                                              |

|-----------------------------------------------|---------------|--------------|---------------------------|----------------------------------------------|

|                                               | Received Copy | Decoded copy | Bit-by-Bit Majority logic | Error Detection                              |

| C1:<br>11011011                               | 10011011      | 10011011     |                           |                                              |

| C2:<br>10111101<br>(Half-Byte Packet Reverse) | 11111101      | 11111101     |                           | 11011011<br>No<br>(11011011 = Original copy) |

| C3:<br>11011011<br>(Even-odd selection)       | 10011011      | 11001011     |                           |                                              |

Example 5: Original packet is 10110011.

**Table 8. Proposed scheme for the packet 11011011**

| Transmitter                                   | Receiver      |              |                           |                                              |

|-----------------------------------------------|---------------|--------------|---------------------------|----------------------------------------------|

|                                               | Received Copy | Decoded copy | Bit-by-Bit Majority logic | Error Detection                              |

| C1:<br>10110011                               | 10010011      | 10010011     |                           |                                              |

| C2:<br>11011100<br>(Half-Byte Packet Reverse) | 11111100      | 11111100     |                           | 10110011<br>No<br>(10110011 = Original copy) |

| C3:<br>01011101<br>(Even-odd selection)       | 01111101      | 10110111     |                           |                                              |

Example 6: Original packet is 00110011.

**Table 9. Proposed scheme for the packet 00110011**

| Transmitter                                   | Receiver      |              |                           |                                    |

|-----------------------------------------------|---------------|--------------|---------------------------|------------------------------------|

|                                               | Received Copy | Decoded copy | Bit-by-Bit Majority logic | Error Detection                    |

| C1:<br>00110011                               | 01110011      | 01110011     |                           |                                    |

| C2:<br>11001100<br>(Half-Byte Packet Reverse) | 10001100      | 00010011     | 00110011                  | No<br>(0011001<br>1=Original copy) |

| C3:<br>01010101<br>(Even-odd selection)       | 00010101      | 00100011     |                           |                                    |

With the above examples it is illustrated that modified APC with half-byte packet reversed and even-odd selection copy can correct errors which occur in the same bit position in all the received erroneous copies, and also the burst error which occur in regular pattern.

#### 4. RESULTS AND ANALYSIS

The proposed scheme has many desirable properties:

- The proposed scheme can perform some error corrections while it does not add additional bits to the packet. This is different from the traditional concept of forward error correction. Consequently, the proposed scheme does not consume extra bandwidth in the wireless channel.

- As in conventional APC, when error occurs in same location of all the received copies it fails to correct the packet. But with this proposed scheme errors get distributed with the decoding process and we can get the correct packet. As a result correction capability of APC is increased.

In the conventional APC scheme, three copies of a packet is sent and when double bits and single bit error occurs then the correction capability is not affected and it can correct the errors at the receiver side without requesting for retransmission. If  $P_1$ ,  $P_2$  is the probability of packet with single bit and double bit respectively, then it is given by [14]:

$$P_1 = kC_1\alpha_1 (1-\alpha_1)k-1 \quad (1)$$

$$And P_2 = kC_2\alpha_2 (1-\alpha_2)k-2 \quad (2)$$

Where  $k$  is the packet size,  $\alpha$  is bit error rate.

Thus probability of packet in error except double bit and single bit error is given by:

$$P' = P - P_1 - P_2 \quad (3)$$

And correction capability of APC is given by:

$$CAPC = (1 - P') \quad (4)$$

Thus, throughput efficiency of APC with double bit error is given by:

$$\eta_{APC} = (3P_2 + (P' / (1 - P'))) \quad (5)$$

where  $P' = P - P_1 - P_2$  and the first part of equation (5) is for conventional APC for correcting double bit error; second part is for normal stop-and-wait ARQ other than double bit error and single bit error.

In the modified technique, the probability of single bit error, double bit error and triple bit errors will be corrected as follows:

If  $P_1$ ,  $P_2$  and  $P_3$  are the probability of packet with single bit, double bit and triple bit error respectively, then receiver will acknowledge without these error is:

$$P = P_1 + 2P_2 + 3P_3 \quad (6)$$

Thus, probability of packet in error except single bit, double bit and triple bit errors is given by:

$$P'' = P - P_1 - P_2 - P_3 \quad (7)$$

Where  $P_1$ ,  $P_2$  and  $P_3$  are the probability of packet with single bit, double bit and triple bit error respectively and  $P_1$ ,  $P_2$  is given as in equations (1) and (2) and  $P_3$  is given as

$$P_3 = kC_3\alpha_3 (1-\alpha_3)k-3 \quad (8)$$

And correction capability of modified APC scheme is given by:

$$CMAPC = (1 - P'') \quad (9)$$

Thus, throughput efficiency or average number of times a packet needs transmission (including retransmission) for successful delivery with triple bit error is given by:

$$IMAPC = (P_1 + 2P_2 + 3P_3 + (P'' / (1 - P''))) \quad (10)$$

Where  $P'' = P - P_1 - P_2 - P_3$  and the first part of equation (10) is for modified APC for correcting triple bit error; second part is for normal stop-and-wait ARQ with bit errors other than triple bit, double bit and single bit error.

#### 5. CONCLUSION

In the traditional APC, transmitters transmit the three copies of the original packet. If error occurs in these three copies at the same bit location then APC fails to correct it. This limitation is overcome in this paper by using the new technique where half byte packet reversal logic and even and odd selection method is applied. In this paper, it can be concluded that when modification was done using half byte reversal in the second copy and even & odd selection method in the third copy then the improvement in the correction capability of the conventional APC was observed. Thus, throughput increases and bandwidth utilization decreases as number of retransmissions get reduces. In future, simulation results of the proposed technique and conventional APC will be evaluated and compared to show the superiority of the proposed technique over conventional APC.

#### 6. ACKNOWLEDGMENTS

On the very outset of this report, we would like to extend our sincere & heartiest obligation towards all the persons who have helped us in this endeavor. Without their active guidance, help, co-operation & encouragement, we would not have made headway in this paper.

## 7. REFERENCES

- [1] Yiu-Wing Leung, 2000. Aggressive Packet Combining for error control in wireless networks, trans. Comm vol. E83, No 2 , pp38-385.

- [2] C T Bhunia, 2010. Modified Aggressive Packet Combining Scheme. Pre-print, ICTP, Italy, IC/2010/037 pp. 1-10.

- [3] Y. Bulo, S. K. Chakraborty, C. T. Bhunia, 2014. New Protocol of Aggressive Packet Combining Scheme. International Journal of Computer Applications, USA, (0975-8887), Volume 85-No. 6 pp-17-20.

- [4] Y. Bulo, C. T. Bhunia, 2015. New Protocol of Aggressive Packet Combining Scheme: An extension to throughput comparison. International Journal of Computer Applications, USA (0975 8887) Volume 113 No. 5 pp- 5-8.

- [5] Sanjit Ningthoujam, Swarnendu K Chakraborty and Chandan T Bhunia, 2014. New modified technique of Aggressive packet combining scheme with multiple routes selection to get high error correction and throughput. International journal of advanced electronics and communication systems, vol.3 Oct-Nov.

- [6] S. K. Chakraborty, R. S. Goswami, A. Bhunia, C. T. Bhunia, 2015. Investigation of Two New Protocols of Aggressive Packet combining scheme in achieving better throughput. Journal of the Institute of Engineers (India) B Springer,DOI: 10.1007/s40031-014-0135-7.

- [7] S. K. Chakraborty, R. S. Goswami, A. Bhunia, C. T. Bhunia, 2014. Two New Protocols for Improving Performance of Aggressive Packet Combining Scheme.

- [8] International Journal of Current Science & Technology. ISSN NO: 23205636, Vol.-1, No.-1, pp- 161-165.

- [9] C T Bhunia, 2005. Information Technology Network and Internet. New Age International Publishers, First Edition.

- [10] C T Bhunia, 2007. Packet Reversed Packet Combining Scheme. Proc. IEEE Computer soc., CIT, Aizu University, Japan, pp 447-451.

- [11] C T Bhunia, 2005. Modified Packet combining using error forecasting decoding to control error. International Conference on Information Technology and Applications (ICITA), ISBN: 0-7695-2316-1, Vol. 2, pp. 641 – 646.

- [12] S B Wicker, 1991. Adaptive rate error control through the use of diverse combining and majority logic decoding in hybrid ARQ protocol, IEEE Trans Comm., Vol.39. No. 3, pp 380-385.

- [13] B. Han, L. Ji, S. Lee, B. Bhattacharjee, and R. Miller, 2012. Are All Bits Equal?Experimental Study of IEEE 802.11 Communication Bit Errors" IEEEACM transactions on Networking, Vol. 20, No.6, pp. 1695-1706.

- [14] A. Miu, H. Balakrishnan, and C. E. Koksal, 2005. Improving loss resilience with multi-radio diversity in wireless networks," in Proc. MobiCom, pp. 1630.

- [15] Prajit Paul, Asok Kumar and Krishna Chandra Roy, 2010. Throughput Analysis on a Scheme of Product Codes for ARQ Protocol. 15th IEEE International Workshop on Computer Aided Modeling, Analysis and Design of Communication Links and Networks (CAMAD), pp. 36-40,