# **Automatic Synthesis of Reversible Circuits**

Swanti Satsangi Department of Physics and Computer Science Dayalbagh Educational Institute Agra, India C. Patvardhan Department of Electrical Engineering Dayalbagh Educational Institute Agra, India P.K. Kalra Department of Computer Science and Engineering Indian Institute of Technology Delhi, India

# ABSTRACT

The design of reversible systems significantly differs from their conventional counterparts therefore Evolutionary algorithms have been explored in the past for the purpose. In this work, the Enhanced Quantum inspired Evolutionary algorithm is employed for synthesis of various digital and benchmark circuits and its comparative performance analysis with other evolutionary algorithms as well as existing search and optimization techniques is presented. It is shown that the proposed enhanced Quantum inspired Evolutionary algorithm not only possesses a better exploration capacity but also performs faster than other techniques.

## **Keywords**

Evolutionary Algorithms, Quantum Inspired Evolutionary Algorithm, Reversible Circuit Synthesis, Quantum Circuits, Binary to Gray Code Converters.

# 1. INTRODUCTION

Digital circuits deal with digital information represented by binary values called bits. These circuits perform various combinational and sequential operations with the help of logical gates like AND, OR, NOT, XOR etc. Among the varied tasks that digital circuits perform, the most common are the arithmetic and logical operations such as addition, subtraction, multiplication, division, parity calculation, comparison, code conversion etc. Conventional digital circuits are made up of irreversible logic gates that cause loss of energy due to loss of information in every operation. The energy expense in the current CMOS technology is mainly due to two reasons; one due to the power consumed by the chips and the other due to the loss of information in every calculation. Landauer's principle states that for every bit of digital information that is lost in computation, there is a loss of at least kTln2 joules of energy (k is Boltzmann constant and T is the operating temperature). The second issue of information loss can be dealt with by making use of reversible logic while the first component relies more on technology [18] [19].

With the advent of low power computing technologies like Quantum, Nano and optical computing it has been shown that lossless computation is possible if the circuits are completely reversible causing no loss of information whatsoever [20]. The focus of modern digital circuit designing has now shifted towards replacing irreversible circuits with low power lossless reversible circuits [6]. This reversibility in conventional computing can be introduced by maintaining the number of outputs same as the number of inputs by making use of reversible gates [2] [13] [20] [10]. This reversible logic finds applications in fields like VLSI design, Quantum Computing, Optical computing, DNA computing, Nanotechnology etc.

Designing digital circuits involves knowledge of a lot of parameters like types of gates, fan-ins, fan-outs, logical inputs

and outputs, rules etc. Simple digital circuits can be derived manually or by conventional methods but as the complexity and size of circuits increases, conventional methods for designing circuits become time consuming and at times fail to give accurate results [7]. Therefore, the absence of a standard algorithmic approach makes the designing of these circuits difficult. Miller et al. reported a Genetic algorithm which is capable of evolving a number of arithmetic circuits including reversible adders and multipliers [17]. Chen et al. presented an efficient graph-based Evolutionary optimization technique for designing reversible arithmetic circuits [3]. Li et al. [14] proposed a best-path search algorithm based on ACO (Ant Colony Optimization) for reversible logic synthesis. This method was suitable for handling large reversible functions and is able to generate either optimal or near-optimal circuits with less gate counts. Lukac et al. proposed automated synthesis of reversible circuits using GA. Their emphasis is on better problem encoding which results in providing better solutions. They have also developed a Parallel Genetic Algorithm for constructing Boolean reversible circuits using several Quantum gates on qudits with various radices [16]. Datta et al. [4] introduced a PSO (Particle Swarm Optimization) based search technique for synthesis of a reversible logic circuit. The algorithm obtains near optimal solutions without exploring the entire search space. Eftakhar et al. applied genetic programming with subtree mutation for evolving common RL arithmetic circuits [7].

Despite the manifold progress in the field of reversible circuit synthesis, designing these circuits is still a problem and requires a systematic automated technique. Most of the existing techniques either involve complex arithmetic algorithms or are based on Evolutionary optimization techniques like Evolutionary graph generation [1][7].

Enhanced Quantum Inspired Evolutionary Algorithm (EQIEA) was proposed by the authors [28] for automatic generation of reversible circuit and was shown to be superior to QIEA on some reversible circuit generation problems. This provides the motivation for further study on a larger variety of problems including benchmark problems presented in literature so as to enable comparison of performance with other reported strategies. In this paper an attempt is made to compare the performance of EIQEA with earlier attempts on benchmark problems. Further, it has been shown that the proposed algorithm fairs better than other Evolutionary algorithms as well as existing techniques for reversible circuit synthesis. It is demonstrated that the algorithm is able to generate better circuits for a variety of problems in lesser time.

The paper has been organized as follows. Section 2 discusses the salient features of reversible logic and how it is different from conventional irreversible logic. Section 3 provides a pseudo code for the proposed EQIEA. Section 4 illustrates the various benchmark circuit obtained using the algorithm and section 5 gives a comparison of the obtained circuits with previous techniques. Sections 6 and 7 show the comparative analysis of EQIEA with other existing techniques for reversible circuit synthesis and Evolutionary algorithms respectively. section 8 finally summarizes the findings of the paper.

## 2. REVERSIBLE LOGIC CIRCUITS

A circuit composed of reversible gates is always reversible. Quantum gates like CNOT, Toffoli, rotation gates etc. are examples of reversible gates. These gates, when used with bits as inputs in place of qubits, act as classical reversible gates thus rendering the classical circuits reversible. Classical reversible circuits can thus be considered as a subset of Quantum circuits and are sometime also termed as Quantum equivalents of classical circuits [26]. There is also a great extent of similarity between designing Quantum and classical reversible logic circuits.

In conventional classical circuits it is impossible to uniquely retrieve information about the inputs from the output. In reversible classical circuits this is possible. The unique feature of Reversible logic (RL) is that no information is lost. Researchers have shown that it is possible to make a classical circuit reversible by making use of additional bits in the input and/or output known as ancilla and garbage bits [18]. Both ancilla and garbage bits facilitate in maintaining the reversibility in RL circuits but do not perform any operation.

The main differences between RL circuits and irreversible circuits are:

- Traditional irreversible circuits can have any number of fan-outs while in RL circuits fan out is not allowed which essentially means that no qubit can be copied.

- Reversible circuits must always be planar and no feedbacks and loops are allowed.

These thumb rules help in maintaining reversibility in RL circuits. However, the main difference between RL Circuits and Quantum Logic (QL) circuits is that in RL circuits, constant values can be introduced on some inputs in order to modify the functionality of the circuit whereas this is not done in QL circuits. These constant inputs can then, in principle, be reinserted back into the power supply and thus do not cause any energy dissipation. While synthesizing the RL circuits, following should be kept in mind [15]:

Over-use of ancilla and garbage bits should be avoided since each extra bit contributes to energy

dissipation and the purpose of RL is to reduce loss of energy

Higher number of fan-outs should be avoided since each time the output of a gate is used as input to an additional gate, a copying circuit is required.

## 3. ENHANCED QUANTUM INSPIRED **EVOLUTIONARY ALGORITHM**

The EQIEA has been described in detail in earlier work by the authors [28]. The pseudo-code for the EQIEA is given as follows.

- $t \leftarrow 0$ 1.

- 2. Initialize Quantum population Q(t)

- 3. Make gray-coded population P(t) from Q(t)

- 4. Evaluate P(t)

- 5. Copy P(t) to local best solution B(t)

- Assign the fittest B(t) to global best b 6.

- 7. Update Q(t) towards b 8.

- while termination condition not satisfied

- a.  $t \leftarrow t + 1$

- b. Make P(t) from updated Q(t) c.

- Evaluate P(t)

- d. Compare P(t) with B(t-1)

- i. Copy P(t) to B(t) if better than B(t-1)

- Assign the fittest B(t) to global best b e. f.

- Repair b

- Permute b i.

- if b(t-1) fitter, retain b else ii. replace

- iii. Substitute in B(t)

- Update Q(t) towards modified B(t) g.

- if t > 1000 9

- 10. Purge non-performing individuals

- 11. End

# 4. EXPERIMENTS ON BENCHMARK CIRCUITS

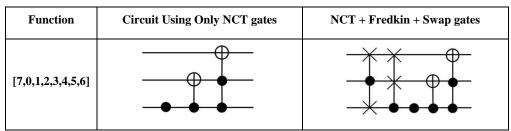

Several 3-bit random circuits from the Revlib benchmark database [21] were evolved using EQIEA for the purpose of comparison with existing search algorithms. Two types of gate libraries have been utilized. The first one consists of only NOT, CNOT and Toffoli gates. This library is the same as the ones reported earlier in literature. The second library has additional Swap and Fredkin gates. The evolved circuits have been given in Table 1.

#### **Table 1. Benchmark Circuits Evolved Using EQIEA**

# 5. COMPARISON OF EQIEA WITH OTHER ALGORITHMS ON BENCHMARK CIRCUITS

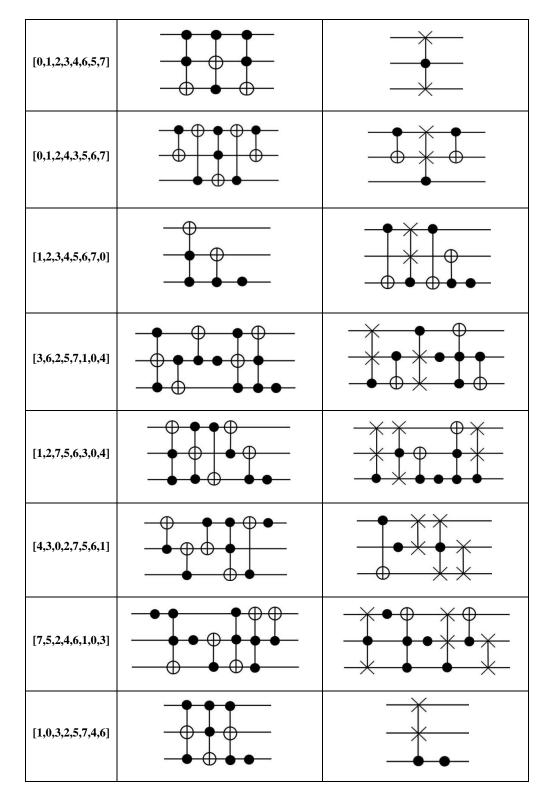

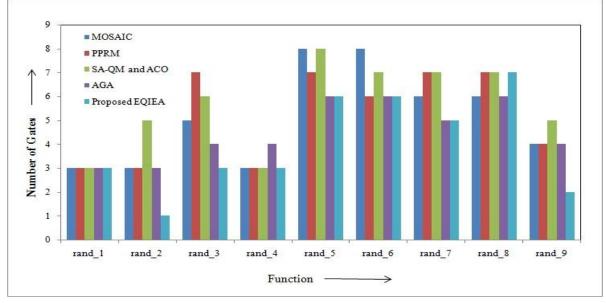

Table 2 gives a gate count comparison of EQIEA with four other existing techniques namely Moving Forward Synthesis Algorithm (MOSAIC) [22], Positive Polarity Reed-Muller expression (PPRM) [9], Simulated Annealing Based Quine -McCluskey Method with Ant Colony Optimization (SA-QM and ACO) [24]and Adaptive Genetic Algorithm (AGA) [25]. In initial experiments performed using NCT (NOT, CNOT, Toffoli) gates library, EQIEA is found to evolve solutions with least number of gates for all the circuits from among the existing algorithms. Further, on including Fredkin and Swap gates forming the second library, optimum solutions were obtained with minimum number of gates.

Further, a bar graph shown in Figure 1 comparing the above mentioned five algorithms is plotted for all the evolved random functions. The proposed algorithm can be seen to obtain smallest gate count for all functions.

|                  | Function          | No. of Gates |      |           |     |                |                  |  |

|------------------|-------------------|--------------|------|-----------|-----|----------------|------------------|--|

| Function<br>Name |                   | MOSAIC       | PPRM | SA-QM and | AGA | Proposed EQIEA |                  |  |

|                  |                   |              |      | ACO       |     | NCT<br>gates   | NCT +<br>Fredkin |  |

| rand_1           | [7,0,1,2,3,4,5,6] | 3            | 3    | 3         | 3   | 3              | 5                |  |

| rand_2           | [0,1,2,3,4,6,5,7] | 3            | 3    | 5         | 3   | 3              | 1                |  |

| rand_3           | [0,1,2,4,3,5,6,7] | 5            | 7    | 6         | 4   | 5              | 3                |  |

| rand_4           | [1,2,3,4,5,6,7,0] | 3            | 3    | 3         | 4   | 3              | 5                |  |

| rand_5           | [3,6,2,5,7,1,0,4] | 8            | 7    | 8         | 6   | 7              | 6                |  |

| rand_6           | [1,2,7,5,6,3,0,4] | 8            | 6    | 7         | 6   | 6              | 6                |  |

| rand_7           | [4,3,0,2,7,5,6,1] | 6            | 7    | 7         | 5   | 6              | 5                |  |

| rand_8           | [7,5,2,4,6,1,0,3] | 6            | 7    | 7         | 6   | 7              | 7                |  |

| rand_9           | [1,0,3,2,5,7,4,6] | 4            | 4    | 5         | 4   | 4              | 2                |  |

### Table 2. Gate count comparison of EQIEA with MOSAIC, PPRM, SA-QM with ACO and AGA

Figure 1 : Comparison of Proposed EQIEA With Existing Algorithms

| Table 3 : Comparison of Evolved Binary-Gray Converter | <b>Circuits with Existing Circuits</b> |

|-------------------------------------------------------|----------------------------------------|

|-------------------------------------------------------|----------------------------------------|

| Circuit                 | Reference              | No. of<br>gates | No. of<br>ancillary<br>inputs | No. of<br>garbage<br>outputs | Gates                                    |

|-------------------------|------------------------|-----------------|-------------------------------|------------------------------|------------------------------------------|

|                         | Gandhi et al. [8]      | 3               | 4                             | 4                            | CNOT                                     |

| Binary -                | Sarvanan et al.[23]    | 3               | 3                             | 3                            | CNOT, URG (Universal<br>Reversible Gate) |

| Gray code<br>converters | Haghparast et al. [11] | 3               | 3                             | 2                            | CNOT, F2G (Feynman<br>Double Gate)       |

|                         |                        | 3               | 0                             | 0                            | CNOT                                     |

|                         | Proposed EQIEA         | 3               | 0                             | 0                            | CNOT                                     |

# 6. COMPARISON OF EQIEA WITH EXISTING RL CIRCUIT SYNTHESIS ALGORITHMS

Apart from benchmark circuits, 3, 4, 5, 6, 7 and 8 bit Binary to Gray and Gray to Binary code converter circuits were evolved using EQIEA. A number of attempts in designing Binary-to-Gray code converters have been made earlier but none of these has been done using evolutionary techniques. A comparison of these with the results in this paper has been given in Table 3 (for 4-bit converter).

In the proposed work, Binary - Gray code conversion circuits have been designed without the use of ancilla and garbage bits. All the other circuits, except the one proposed by Haghparast et al. [11] using CNOT, make use of ancillary and garbage bits. It is evident that the circuits evolved using EQIEA are simpler in terms of gates used and smaller in terms of number of gates.

# 7. COMPARISON OF EQIEA WITH EXISTING EVOLUTIONARY ALGORITHMS

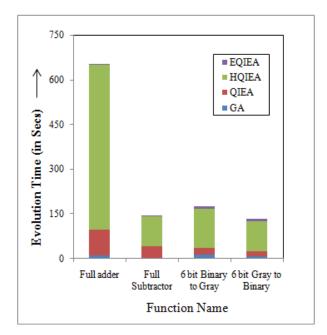

For the purpose of comparative analysis of EQIEA with other Evolutionary algorithms, a variety of circuits ranging from arithmetic, logic, Boolean and code converters, were evolved using three other Evolutionary algorithms namely genetic algorithm [26] Quantum inspired Evolutionary algorithm (QIEA) [12] [28] and hybrid Quantum inspired evolutionary algorithm (HOIEA) [5] [27]. It was observed that all algorithms including EQIEA were able to find solutions for all the circuits with upto 6 bits. For circuits with upto 8 bits, only EQIEA was able to converge while the other algorithms failed to converge for circuits with more than 6 bits. This means that EQIEA is able to solve problem of the matrix size 2^8 x 2^8. Further, although the circuits obtained using all the algorithms were identical, EQIEA was found to outperform all the three algorithms for all functions in terms of the evolution time. GA is the second best algorithm for the given purpose while HQIEA took the maximum time. Figure 2 shows the comparison of evolution times using the four algorithms.

## 8. CONCLUSION

An Enhanced- Quantum inspired Evolutionary algorithm has been proposed in this work for reversible circuit synthesis.

A comparison of the proposed EQIEA with other search and optimization techniques like Ant Colony Optimization (ACO), Particle Swarm Optimization (PSO), Adaptive Genetic Algorithm (AGA) and Moving forward Synthesis Algorithm (MOSAIC) on benchmark circuits has been performed and it has been shown that the proposed algorithm performs better than the other algorithms in most cases except a few where its performance is at par with the best.

A comparison of the proposed EQIEA has been done with the existing Evolutionary algorithms i.e. GA, QIEA and HQIEA. It is shown that EQIEA not only performs faster but also possesses a better exploration capacity. It has also been shown that GA, QIEA, HQIEA and EQIEA, all are able to find good solutions for a given problem, but EQIEA typically does so in much lesser time.

It has thus been experimentally shown that the proposed EQIEA is a good algorithm for problem of reversible logic circuits synthesis.

Figure 2 : Comparison of Evolution time using GA, QIEA, HQIEA and EQIEA

## 9. REFERENCES

- Aoki T., Homma N., and Higuchi T., 2003, Evolutionary Synthesis of Arithmetic Circuit Structures, Artificial Intelligence Review, Vol. 20, pp. 199–232.

- [2] Bruce J. W., Thornton M. A., Shivakumaraiah L., Kokate P. S., and Li X., 2002, Efficient adder circuits based on a conservative reversible logic gate, Proceedings of IEEE Symposium on VLSI, pp. 83–88.

- [3] Cheng K. W. and Tseng C. C. , 2002, Quantum full adder and sub-tractor, Electronics Letters, Vol. 38, No. 22, pp. 1343–1344.

- [4] Datta K., Sengupta I., 2012, and Rahaman H., Reversible circuit synthesis using evolutionary algorithm. In 5th International Conference on Computers and Devices for Communication (CODEC), pp 1–4.

- [5] Ding S., Jin Z. and Yang Q. ,2008, Evolving quantum circuits at the gate level with a hybrid quantum-inspired evolutionary algorithm, Journal of Soft Computing.

- [6] Dubey V., Singh O. P., Mishra G.R., 2012, Design and Implementation of a Two-Bit Binary Comparator using Reversible Logic, International Journal of Scientific and Research Publications, Vol. 2, No 7.

- [7] Eftakhar S. M. A, Habib S. K. M. and Hashem M. M. A., 2013, Evolutionary Design of Digital Circuits Using Genetic Programming.

- [8] Gandhi M. and Devishree J., 2013., Design of Reversible Code Converters for Quantum Computer based Systems, International Journal of Computer Applications, No. 3.

- [9] Gupta N. J. P. and Agrawal A., 2006, An algorithm for synthesis of reversible logic circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 25, pp. 2317–2330.

- [10] Haghparast M., Jassbi S., Navi K., and Hashemipour O., 2008, "Design of a novel reversible multiplier circuit using HNG gate in nanotechnology, World Applied Science Journal, Vol. 3, No. 6, pp. 974–978.

- [11] Haghparast M., Hajizadeh M., Hajizadeh R. and Bashiri R., 2011, On the Synthesis of Different Nanometric Reversible Converters, Middle-East Journal of Scientific Research, Vol. 7, No. 5, pp. 715-720.

- [12] K. H. Han and J. H. Kim, 2002, Quantum-Inspired Evolutionary Algorithm for a Class of Combinatorial Optimization, IEEE Transactions On Evolutionary Computation, Vol. 6, No. 6.

- [13] Khan M., 2002, Design of full-adder with reversible gates, Proc. International Conference on Computer and Information Technology, pp. 515–519.

- [14] Li M, Zheng Y., Hsiao M. S, Huang C., 2010, Reversible logic synthesis through ant colony optimization. Design Automation Test in Europe, pp. 208–212.

- [15] Lukac, M., Perkowski, M., 2002, Evolving quantum circuits using genetic algorithm. Proceedings of the NASA/DOD Conference on Evolvable Hardware.

- [16] Lukac M., Perkowski M. and Kameyama M., 2011, Evolutionary Quantum Logic Synthesis of Boolean Reversible Logic Circuits Embedded in Ternary Quantum Space using Heuristics, arxiv: 1107.3383v1, [quant-ph].

- [17] Miller J. F, Thompson P. and Fogarty T. C., 1997, Designing electronic circuits using Evolutionary Algorithms. Arithmetic Circuits: A case study, Recent Advancements and Industrial Applications, John Wiley & Sons.

- [18] Nielson M. A. and Chuang I. L. 2000, Quantum Computing and Quantum Information. Cambridge University Press.

- [19] Plenio M. B. and Vitelli V., 2001, The physics of forgetting: Landauer's erasure principle and information theory, Contemporary Physics, Vol. 42, No. 1, pps 25-60.

- [20] Rentergem V. and Vos, A., 2005, Optimal design of a reversible full adder. International Journal of Unconventional Computing, Vol. 1, No. 4, pp. 339.

- [21] Online resource for reversible benchmark: http://www.revlib.org/

- [22] Saeedi M. S. Z. M. and Sedighi M., 2008, Moving forward: A non-search based synthesis method toward efficient cnot-based quantum circuit synthesis algorithms. ASPDAC, pp. 83–88.

- [23] Saravanan M., Suresh K. and Uma S., 2013, Novel Reversible Code Converters Using Reversible Logic Gates, International Journal of Electrical and Electronics, Engineering Research, Vol. 3, No. 3, pp. 161-166.

- [24] Sarkar, M., Ghosal, P., and Mohanty, S. P., 2013, Reversible circuit synthesis using aco and sa based quine-mccluskey method. In International Midwest Symposium on Circuits and Systems, pp. 416-419.

- [25] Sasamala T. N., Singh A. K. and Mohan A., 2015, Reversible Logic Circuit Synthesis and Optimization using Adaptive Genetic Algorithm, 4thInternational Conference on Eco-friendly Computing and Communication Systems, Procedia Computer Science, Vol. 70, pp. 407 – 413.

- [26] Satsangi S., Gulati A., Kalra P. K, and Patvardhan C., 2012, Application of Genetic Algorithms for Evolution of Quantum Equivalents of Boolean Circuits, International Journal of Electrical, Computer, Electronics and Communication Engineering, Vol. 6, No. 3, 275 -279.

- [27] Satsangi S. and Patvardhan C., 2015, Design of Reversible Quantum Equivalents of Classical Circuits Using Hybrid Quantum Inspired Evolutionary Algorithm, Advanced Computing Conference, pp. 258-262.

- [28] Satsangi S. and Patvardhan C., 2016, Enhanced Quantum Inspired Evolutionary Algorithm For Automatic synthesis of Reversible Circuits, International Journal of Engineering Technology Science and Research, Volume 3, Issue 1, pp. 34 - 45.